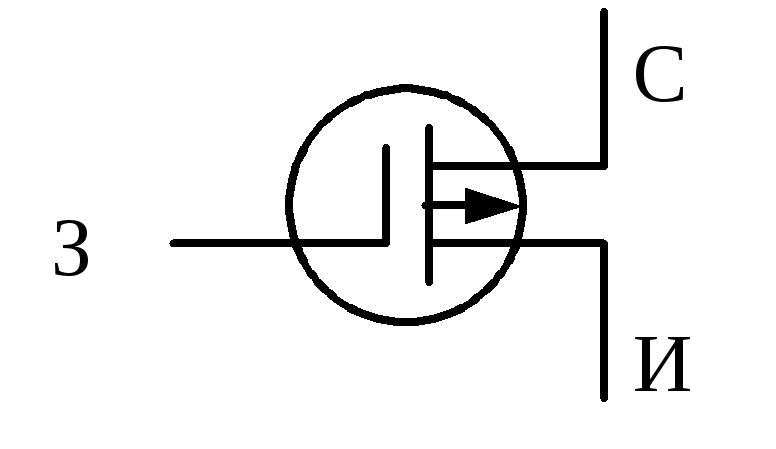

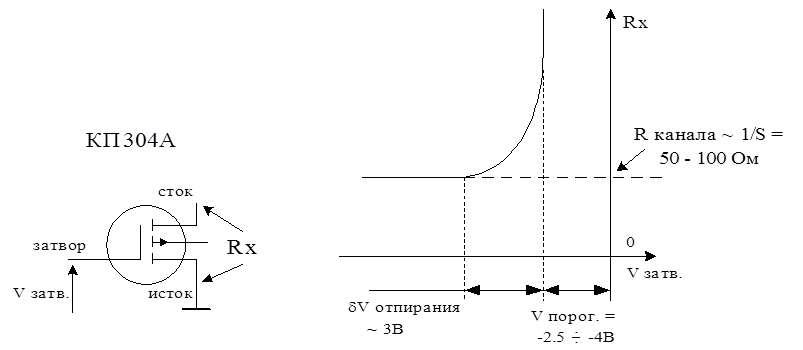

Условные обозначения полевых транзисторов

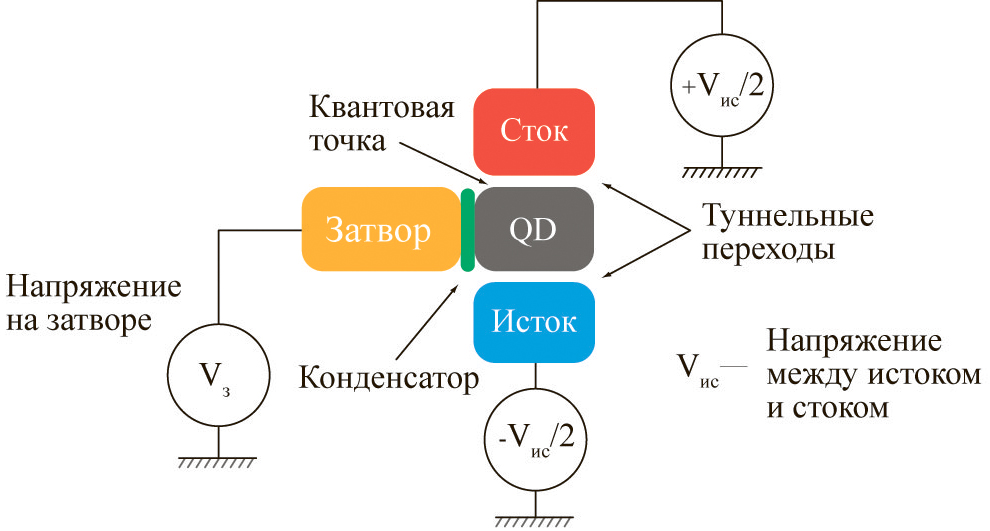

В электронике полевым транзистором называется электронный компонент, в котором ток проходящий через канал регулируется электрическим полем, образующимся в результате подачи напряжения между его истоком и затвором. Основным отличием полевого транзистора от транзистора биполярного является то, что выходное и входное сопротивление у него существенно выше.

Плевые транзисторы нередко именуют униполярными, поскольку основным принципом их действия является перемещение при помощи поля носителей зарядов одного и того же типа. Конструктивно эти приборы представляют собой изготовленные из полупроводниковых материалов пластинки одного типа проводимости, на противоположных сторонах которых способом диффузии создается область другого типа проводимости. На их границах образуется обладающий большим сопротивлением p—n-переход.

В полевых транзисторах существуют области полупроводника которые называют каналами.

Структура полевого транзистора

с управляющим p—n-переходом и каналом n-типа

В случае, если между p-областью и n-областью приложить некоторое напряжение Uзи., как показано на рисунке выше, то p—n-переход окажется включенным в обратном направлении, следовательно его толщина увеличится, а толщины канала уменьшается. При этом принято p-область называть затвором Ucи., то через него начнёт протекать ток в направлении от нижнего к верхнему участку n-области. Часть этой области, от которой основные носители зарядов начинают свое движение, называется истоком, а та часть, по направлению к которой они перемещаются – стоком.

Что касается величины тока, который протекает через канал, то определяющим для нее является сопротивление. Оно, в свою очередь, напрямую зависит от толщины канала. Таким образом, если изменяется величина приложенного к каналу напряжения, то вслед за этим происходит изменение величины тока.

В тех случаях, когда для производства этого электронного компонента в качестве основы берут полупроводник p-типа, то получается полевой транзистор, имеющий канал р-типа и управляющий p—n-переход. Канал в нем образуется n-областью.

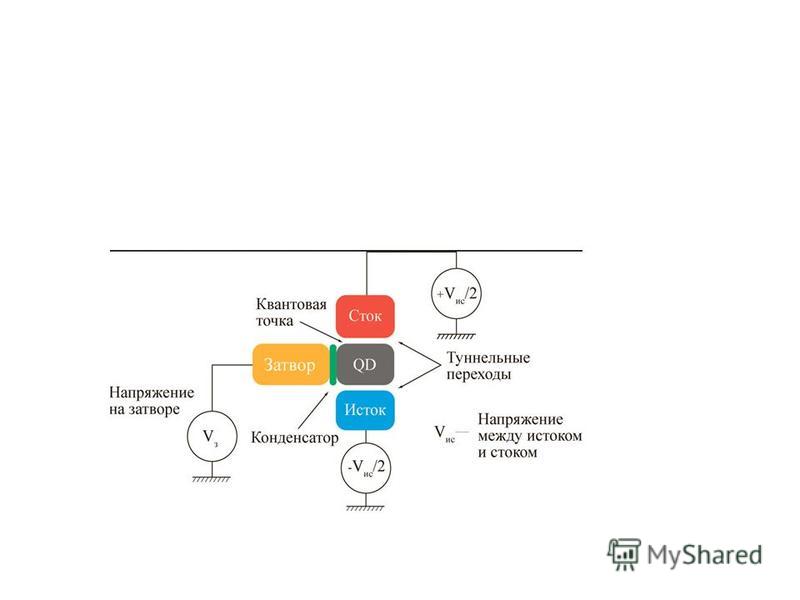

Структура и схема подключения МДП-транзистора

с индуцированным каналом

Полевые транзисторы с изолированным затвором

Помимо тех полевых транзисторов, которые имеют в своей конструкции управляющий затвор, имеются и такие, у которых он изолирован. В электронике для обозначения таких транзисторов используют аббревиатуры МДП (металл-диэлектрик-полупроводник). Соответственно, такие приборы называют

Соответственно, такие приборы называют МОП-транзисторами или МДП-транзисторами.

Для МДП—транзистора характерно то, что в нем между истоком и стоком располагается n-область, представляющая собой подложку. Поэтому образуется два p—n-перехода, которые включены навстречу друг другу. При этом вне зависимости от того, какую именно полярность имеет питающее напряжение, один из этих переходов всегда закрыт, так что в в направлении «исток-сток» ток равен нулю.

Если на затвор подается отрицательное напряжение, то ток в цепи начинает течь. Дело в том, что на расположенные в подложке электроны действует электрическое поле, и они начинают передвигаться вглубь нее.

Существует некоторое пороговое значение напряжения, при котором количество дырок, расположенных у самой поверхности подложки, становится существенно больше, чем электронов. В результате этого происходит так называемая инверсия типа электроповодности: она обретает p-тип. В результате этого между стоком и истоком получается канал, связывающий их. Его толщина зависит от того, какое именно значение имеет приложенное напряжение. Если изменять его, то можно регулировать и толщину канала, поскольку сопротивление участка, располагающегося между истоком и стоком, также будет изменяться.

В результате этого между стоком и истоком получается канал, связывающий их. Его толщина зависит от того, какое именно значение имеет приложенное напряжение. Если изменять его, то можно регулировать и толщину канала, поскольку сопротивление участка, располагающегося между истоком и стоком, также будет изменяться.

Обозначения полевых транзисторов на схеме

Разработка моста для режима жестких переключений на нитрид-галлиевых транзисторах Transphorm

16 июня 2017

Компания Transform произвела настоящую революцию в схемотехнике силовых преобразовательных устройств, представив на рынке мощные каскодные GaN-транзисторы на кремниевой подложке. Это позволило начать применение мостовых схем с жесткой коммутацией, в которых уменьшено и сопротивление в открытом состоянии, и емкость затвора, а КПД достигает 99%.

Согласно аналитическим прогнозам, мировой доход от продаж силовых полупроводниковых приборов (п/п), изготовленных по технологиям SiC (карбид кремния) и GaN (нитрид галлия), вырастет к 2025 году до 3,7 млрд. долларов США по сравнению с 210 млн. в 2015 году. Ожидается, что основными областями применения новых технологий будут электротранспорт, в том числе гибридные автомобили, а также источники питания и преобразователи напряжения (инверторы), работающие с фотоэлектрическими батареями. Возрастающий интерес к новым технологиям производства силовых п/п обусловлен требованиями увеличения КПД и удельной мощности силовых преобразователей. Например, использование GaN-транзисторов производства компании Transphorm в инверторе мощностью 4,5 кВт позволило уменьшить габариты устройства на 40% (рисунок 1) и повысить КПД с 96,5% до 98% по сравнению с инвертором на кремниевых МОП-транзисторах.

долларов США по сравнению с 210 млн. в 2015 году. Ожидается, что основными областями применения новых технологий будут электротранспорт, в том числе гибридные автомобили, а также источники питания и преобразователи напряжения (инверторы), работающие с фотоэлектрическими батареями. Возрастающий интерес к новым технологиям производства силовых п/п обусловлен требованиями увеличения КПД и удельной мощности силовых преобразователей. Например, использование GaN-транзисторов производства компании Transphorm в инверторе мощностью 4,5 кВт позволило уменьшить габариты устройства на 40% (рисунок 1) и повысить КПД с 96,5% до 98% по сравнению с инвертором на кремниевых МОП-транзисторах.

Рис. 1. Инверторы мощностью 4,5 кВт, изготовленные с использованием кремниевых и GaN-транзисторов

Показателем качества, характеризующим различные технологии изготовления высоковольтных ключей для силовой преобразовательной техники, является комбинация максимального напряжения (напряжения пробоя) и удельного сопротивления ключа в открытом состоянии.

Рис. 2. Показатели качества различных технологий изготовления высоковольтных транзисторов

Таблица 1. Сравнительные характеристики различных технологий производства силовых подупроводниковых ключей

| Наименование параметра | Технология производства силовых п/п-ключей | ||

| Si | 4H-SiC | GaN | |

| Максимальная напряженность электрического поля, 106 В/см | 3 | 30 | 30 |

| Подвижность носителей заряда, см2/В•с | 1500 | 700 | 2000 |

| Коэффициент теплопроводности, Вт/см•К | 1,5 | 4,5 | 1,5 |

Особенности применения GaN-транзисторов в мостовых схемах

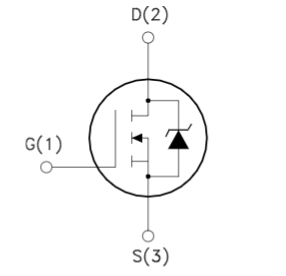

Широкому применению GaN-транзисторов до недавнего времени препятствовали технологические трудности получения нитрид-галлиевых структур, а также инверсная логика управления – поскольку базовая структура GaN-транзистора является нормально открытым ключом. Силовые высоковольтные ключи производства компании Transphorm представляют собой каскодную структуру, состоящую из нормально-закрытого низковольтного МОП-транзистора и высоковольтного GaN-транзистора с высокой подвижностью электронов (рисунок 3). Благодаря этому для управления GaN-транзисторами Transphorm могут использоваться такие же драйверы затвора, как и для обычных транзисторов с изолированным затвором.

Силовые высоковольтные ключи производства компании Transphorm представляют собой каскодную структуру, состоящую из нормально-закрытого низковольтного МОП-транзистора и высоковольтного GaN-транзистора с высокой подвижностью электронов (рисунок 3). Благодаря этому для управления GaN-транзисторами Transphorm могут использоваться такие же драйверы затвора, как и для обычных транзисторов с изолированным затвором.

Рис. 3. Каскодный GaN-транзистор производства компании Transphorm: а) внутренняя структура; б) эквивалентная схема в виде нормально-закрытого ключа

Работа GaN-транзисторов в мостовой схеме без антипараллельных диодов

Особенность мощных кремниевых МОП-транзисторов – наличие в их структуре паразитного p-n-перехода, который при работе транзистора в мостовой схеме способен проводить ток в паузах между импульсами коммутации, то есть выполнять функции антипараллельного диода. Однако при прохождении тока через внутренний диод МОП-транзистора в его p-n-переходе происходит накопление неосновных носителей заряда, в результате чего при коммутации МОП-транзистора в цепи «сток-исток» образуются импульсы обратного тока восстановления диода. Эта проблема особенно актуальна в высоковольтных мостовых схемах, где паразитный внутренний диод МОП-транзистора при прямом прохождении тока накапливает значительный заряд, что приводит к большой амплитуде импульсов обратного тока и длительному времени рассасывания неосновных носителей в p-n-переходе внутреннего диода. В традиционных мостовых схемах, выполненных на транзисторах с изолированным затвором, параллельно внутреннему диоду устанавливают внешний быстродействующий антипараллельный диод (рисунок 4а), что увеличивает габариты печатной платы и стоимость изделия.

Эта проблема особенно актуальна в высоковольтных мостовых схемах, где паразитный внутренний диод МОП-транзистора при прямом прохождении тока накапливает значительный заряд, что приводит к большой амплитуде импульсов обратного тока и длительному времени рассасывания неосновных носителей в p-n-переходе внутреннего диода. В традиционных мостовых схемах, выполненных на транзисторах с изолированным затвором, параллельно внутреннему диоду устанавливают внешний быстродействующий антипараллельный диод (рисунок 4а), что увеличивает габариты печатной платы и стоимость изделия.

Рис. 4. Полумостовая схема: а) на обычных транзисторах с изолированным затвором; б) на и каскодных GaN-транзисторах Transp

В гибридных каскодных ключах производства компании Transphorm нитрид-галлиевый транзистор выполнен на основе чистого беспримесного полупроводникового материала, вследствие чего в нем отсутствует паразитный p-n-переход и в канале может протекать в обоих направлениях ток, состоящий только из основных носителей. При работе в мостовой схеме ток в паузе между импульсами коммутации протекает через паразитный диод внутреннего МОП-транзистора, однако инжектируемый в него заряд имеет малую величину благодаря низкому рабочему напряжению МОП-транзистора. Вследствие этого нитрид-галиевые транзисторы Transphorm с высокой подвижностью электронов (HEMT) представляют собой практически идеальные ключевые элементы для мостовых схем благодаря способности коммутировать ток в паузах между импульсами без использования дополнительных антипараллельных диодов (рисунок 4б).

При работе в мостовой схеме ток в паузе между импульсами коммутации протекает через паразитный диод внутреннего МОП-транзистора, однако инжектируемый в него заряд имеет малую величину благодаря низкому рабочему напряжению МОП-транзистора. Вследствие этого нитрид-галиевые транзисторы Transphorm с высокой подвижностью электронов (HEMT) представляют собой практически идеальные ключевые элементы для мостовых схем благодаря способности коммутировать ток в паузах между импульсами без использования дополнительных антипараллельных диодов (рисунок 4б).

На рисунке 5 показано протекание тока в каскодном GaN-транзисторе в трех режимах работы:

- При напряжении «сток-исток» VDS > 0 и напряжении на затворе больше порогового VGS > VTH транзистор открыт в прямом направлении (рисунок 5а). Падение напряжения «сток-исток» в прямом направлении протекания тока определяется формулой 1:

, (1)

где RDS(on),Si и RDS(on),GaN – сопротивление в открытом состоянии МОП- и GaN-транзисторов соответственно.

- Протекание тока в обратном направлении происходит при напряжении VDS < 0, при этом возможны два режима работы в зависимости от напряжения «затвор-исток». При напряжении VGS < VTH (рисунок 5б) МОП-транзистор закрыт и ток протекает через внутренний диод МОП-транзистора и нормально-открытый GaN-транзистор. Падение напряжения «исток-сток» в обратном направлении определяется формулой 2:

, (2)

где VSD-Si – падение напряжения на внутреннем диоде МОП-транзистора, IF – ток истока.

- Падение напряжения «исток-сток» в обратном включении можно уменьшить, подав на затвор МОП-транзистора отпирающее напряжение VGS > VTH (рисунок 5в), при этом падение напряжения «исток-сток» будет определяться формулой 3:

(3)

В качестве примера: при обратном токе IF = 5 А уменьшение падения напряжения «исток-сток» в режиме работы в) по сравнению с режимом работы б) составит примерно 0,8 В. При использовании режима работы в) необходимо обеспечить задержку между выключением одного транзистора полумоста и включением другого («мертвое» время) для предотвращения сквозных токов.

Рис. 5. Протекание тока при трех режимах работы каскодного GaN-транзистора

Современные техпроцессы изготовления кремниевых МОП-транзисторов позволяют сформировать в полупроводниковой структуре p-n-переход, который может выполнять функции антипараллельного диода благодаря пониженному значению заряда обратного восстановления QRR. Однако даже у специальных серий МОП-транзисторов с быстрым внутренним диодом величина Qrr превышает этот же параметр GaN-транзисторов в 20 и более раз при одинаковых сопротивлениях канала в открытом состоянии (рисунок 6).

Рис. 6. Процесс обратного восстановления: а) кремниевого МОП -транзистора, б) каскодного GaN-транзистора производства компании Transphorm (закрашенные области на графиках показывают величину заряда обратного восстановления диода)

Особенности топологии печатных плат

Выходные цепи

Рис. 7. Эквивалентная схема выходных цепей полевых транзисторов с учетом паразитных элементов печатной платы

Паразитные индуктивности цепей затвора и стока значительно влияют на перенапряжения, переходные колебательные процессы и, в целом, на устойчивость работы мостовых схем. Несмотря на малые величины зарядов восстановления каскодных GaN-транзисторов, они все же не равны нулю, и при перезаряде емкостей в цепи стока протекают токи с большой скоростью изменения. Для уменьшения амплитуды переходных колебательных процессов необходимо минимизировать паразитные индуктивности, обозначенные на рисунке 7 как LS1, LD1, LS2 и LD2, используя для этого низкоимпедансные силовые и земляные проводники (полигоны) и размещая фильтрующие конденсаторы как можно ближе к транзисторам. Влияние паразитной индуктивности LOUT при этом незначительно, так как она включена последовательно с индуктивностью нагрузки и в первом приближении просто добавляет к ней некоторую величину. Необходимо также минимизировать длину проводника между истоком верхнего ключа (Q1) и стоком нижнего ключа (Q2), что достигается размещением обоих транзисторов на общем радиаторе «спина к спине», как показано на рисунке 8а. Для уменьшения паразитной индуктивности сток Q1 подключен непосредственно к плюсовой шине питания, а исток Q2 – к шине земли (рисунок 8а).

Несмотря на малые величины зарядов восстановления каскодных GaN-транзисторов, они все же не равны нулю, и при перезаряде емкостей в цепи стока протекают токи с большой скоростью изменения. Для уменьшения амплитуды переходных колебательных процессов необходимо минимизировать паразитные индуктивности, обозначенные на рисунке 7 как LS1, LD1, LS2 и LD2, используя для этого низкоимпедансные силовые и земляные проводники (полигоны) и размещая фильтрующие конденсаторы как можно ближе к транзисторам. Влияние паразитной индуктивности LOUT при этом незначительно, так как она включена последовательно с индуктивностью нагрузки и в первом приближении просто добавляет к ней некоторую величину. Необходимо также минимизировать длину проводника между истоком верхнего ключа (Q1) и стоком нижнего ключа (Q2), что достигается размещением обоих транзисторов на общем радиаторе «спина к спине», как показано на рисунке 8а. Для уменьшения паразитной индуктивности сток Q1 подключен непосредственно к плюсовой шине питания, а исток Q2 – к шине земли (рисунок 8а). Полигоны земли и питания находятся на внутренних слоях печатной платы и на рисунке не показаны. Выходная цепь коммутации образована широким проводником, соединяющим исток Q1 со стоком Q2. Необходимо обратить внимание на то, что GaN-транзисторы HEMT производства Transphorm в корпусе TO220 имеют конфигурацию выводов G-S-D, в отличие от традиционной для МОП-транзисторов конфигурации G-D-S. Расположение вывода истока в средней части корпуса уменьшает паразитную связь между входными и выходными цепями. Высоковольтные фильтрующие конденсаторы SMD размещены на нижней стороне печатной платы (рисунок 8б), что позволяет уменьшить паразитную индуктивность проводников.

Полигоны земли и питания находятся на внутренних слоях печатной платы и на рисунке не показаны. Выходная цепь коммутации образована широким проводником, соединяющим исток Q1 со стоком Q2. Необходимо обратить внимание на то, что GaN-транзисторы HEMT производства Transphorm в корпусе TO220 имеют конфигурацию выводов G-S-D, в отличие от традиционной для МОП-транзисторов конфигурации G-D-S. Расположение вывода истока в средней части корпуса уменьшает паразитную связь между входными и выходными цепями. Высоковольтные фильтрующие конденсаторы SMD размещены на нижней стороне печатной платы (рисунок 8б), что позволяет уменьшить паразитную индуктивность проводников.

Паразитная емкость выходной цепи коммутации, обозначенная на рисунке 7 как COUT, увеличивает коммутационные потери, поэтому необходимо стремиться к уменьшению общей площади проводников, образующих выходную цепь коммутации, не допуская при этом значительного увеличения индуктивности цепи. Типичная 4-слойная плата с расстоянием 0,3 мм между внешним слоем и внутренним земляным полигоном добавляет распределенную емкость примерно 15 пФ/см2, следовательно, при частоте коммутации 100 кГц каждый см² площади проводника добавит P = 1/2•C•V2•fs = 120 мВт коммутационных потерь.

Рис. 8. Пример разводки печатной платы: а) силовые шины, б) размещение фильтрующих конденсаторов

Существенным моментом при разработке печатных плат является использование отдельных земляных полигонов для силовых и сигнальных цепей – они должны соединяться между собой только в одной точке.

Цепи управления

Рис. 9. Эквивалентная схема цепи управления, включающая в себя паразитные индуктивности выводов транзистора и внешних цепей

Для входных цепей, соединяющих выход драйвера и затвор МОП-транзистора, также необходимо минимизировать паразитные индуктивности, особенно индуктивность в цепи истока (LS2 на рисунке 9), которая является общей для силовой цепи и цепи управления. При изменении тока стока dID/dt на его паразитной индуктивности формируется напряжение, которое добавляется последовательно с выходным напряжением драйвера в цепи управления. Вследствие этого для цепи истока необходимо использовать низкоимпедансные проводники печатной платы. Основная проблема состоит в том, что последовательно с индуктивностью проводников включена паразитная индуктивность вывода истока корпуса TO220 (рисунок 6), которую невозможно уменьшить, однако, как будет показано далее, можно оценить ее влияние для минимизации обусловленных ею негативных эффектов.

Рис. 10. Осциллограммы напряжений «сток-исток» Vds и «затвор-исток» Vgs транзистора нижнего плеча (Q2) повышающего преобразователя 200…400 В

В начальном интервале переходного процесса включения транзистора ток стока увеличивается с нуля до величины тока нагрузки (0 < ID < ILOAD), при этом скорость изменения dID/dt определяется током затвора. Поскольку напряжение VDS в этом интервале времени практически не меняется, в токе ID отсутствует составляющая, разряда выходной емкости. На индуктивности истока формируется напряжение V = LdI/dt, которое вычитается из напряжения на затворе. При меньшем значении тока затвора IG переходный процесс dI/dt становится более медленным, вследствие чего уменьшаются напряжение на паразитной индуктивности истока и амплитуды связанных с этой индуктивностью паразитных резонансов. Установка резистора в цепи затвора (ZG на рисунке 10) позволяет уменьшать IG, однако вследствие малой величины емкости обратной связи CRSS каскодной схемы не может обеспечить ограничение скорости изменения напряжения выходной цепи d(VDS)/dt. Обычный способ ограничения разряда CRSS с помощью резистора в цепи затвора малоэффективен, поскольку основная выходная емкость CDS не разряжается через резистор затвора. Более предпочтительным является выбор драйвера затвора с меньшим выходным током для ограничения IG и dI/dt. В процессе включения каскодного GaN-транзистора при достижении током стока величины тока нагрузки (ID > ILOAD), происходит быстрый переходный процесс со скоростью dV/dt порядка 100 В/нс. Емкостной ток COSS, обусловленный изменением напряжения d(VDS)/dt, протекает через паразитную индуктивность истока, вызывая колебательный процесс. Пульсации напряжения на паразитной индуктивности через входную емкость транзистора CISS воздействуют на входную цепь и влияют на изменение тока в ней. Установка небольшой ферритовой бусины SMD в качестве ZG разрывает паразитную емкостную связь и препятствует возникновению колебательных процессов тока затвора, не ухудшая существенно форму импульсов напряжения на затворе. В качестве примера на рисунке 10 показаны осциллограммы напряжений «сток-исток» и «затвор-исток» с ферритовой бусиной, имеющей импеданс 120 Ом на частоте 100 МГц, а на рисунке 11 – результаты моделирования тока затвора с ферритовой бусиной и без нее.

Обычный способ ограничения разряда CRSS с помощью резистора в цепи затвора малоэффективен, поскольку основная выходная емкость CDS не разряжается через резистор затвора. Более предпочтительным является выбор драйвера затвора с меньшим выходным током для ограничения IG и dI/dt. В процессе включения каскодного GaN-транзистора при достижении током стока величины тока нагрузки (ID > ILOAD), происходит быстрый переходный процесс со скоростью dV/dt порядка 100 В/нс. Емкостной ток COSS, обусловленный изменением напряжения d(VDS)/dt, протекает через паразитную индуктивность истока, вызывая колебательный процесс. Пульсации напряжения на паразитной индуктивности через входную емкость транзистора CISS воздействуют на входную цепь и влияют на изменение тока в ней. Установка небольшой ферритовой бусины SMD в качестве ZG разрывает паразитную емкостную связь и препятствует возникновению колебательных процессов тока затвора, не ухудшая существенно форму импульсов напряжения на затворе. В качестве примера на рисунке 10 показаны осциллограммы напряжений «сток-исток» и «затвор-исток» с ферритовой бусиной, имеющей импеданс 120 Ом на частоте 100 МГц, а на рисунке 11 – результаты моделирования тока затвора с ферритовой бусиной и без нее. Как видно из рисунка 11, ферритовая бусина эффективно подавляет высокочастотные пульсации тока затвора и, что критически важно, изменение напряжения VGS в этом случае полностью определяется током через емкость CGS.

Как видно из рисунка 11, ферритовая бусина эффективно подавляет высокочастотные пульсации тока затвора и, что критически важно, изменение напряжения VGS в этом случае полностью определяется током через емкость CGS.

Рис. 11. Результаты моделирования тока затвора: а) с ферритовой бусиной; б) без нее

Особенности переключения каскодного GaN-транзистора

Рис. 12. Паразитные емкости транзистора QL нижнего плеча полумоста в выключенном состоянии, QH находится в ключевом режиме | На рисунке 12 показана эквивалентная схема полумоста в интервале времени, когда происходит коммутация транзистора верхнего плеча, транзистор нижнего плеча закрыт, при этом через него протекает замыкающий ток в паузах между импульсами коммутации. При включении транзистора QH в выходной цепи коммутации (S) появляется напряжение с высокой скоростью изменения dV/dt, которое создает ток IGD, заряжающий емкость CGD транзистора QL. Часть этого тока будет заряжать емкость CGS, увеличивая напряжение на затворе. При достаточно большом отношении CGD/CGS увеличение напряжения VGS может привести к включению нижнего транзистора QL. Однако в каскодных GaN-транзисторах это отношение чрезвычайно мало, например, для TPh4006 CGD = 4,5 пФ, а величина CGS составляет 720 пФ при VGS = 0, и более 2000 пФ во включенном состоянии. При достаточно большом отношении CGD/CGS увеличение напряжения VGS может привести к включению нижнего транзистора QL. Однако в каскодных GaN-транзисторах это отношение чрезвычайно мало, например, для TPh4006 CGD = 4,5 пФ, а величина CGS составляет 720 пФ при VGS = 0, и более 2000 пФ во включенном состоянии. |

Рис. 13. Осциллограммы выключения нижнего транзистора QL. Сверху – вниз: напряжение «сток-исток» с масштабирующим коэффициентом 1:100, ток в индуктивности, внешнее напряжение «затвор-исток» |

Рис. 14. Схема управления затвором каскодного GaN-транзистора с отрицательным напряжением

смещения

Более существенной проблемой, чем емкостная связь через CGD каскодной пары, является емкость CGD_Si низковольтного кремниевого МОП-транзистора. Напряжение «сток-исток» кремниевого МОП-транзистора VDS_Si (рисунок 12) при высокой скорости dV/dt может возрасти до величины -VTH GaN-транзистора. В этом случае отношение CGD_Si/CGS будет иметь значительное влияние. Осциллограммы на рисунке 13 показывают, что при изменении VDS_Si напряжение VGS быстро приближается к пороговому уровню, однако, так как повышение VDS_Si происходит при закрытом GaN-транзисторе, ток стока кремниевого МОП-транзистора, обусловленный увеличением VGS, должен сначала разрядить затвор GaN-транзистора до того, как через транзистор начнет протекать внешний ток. Поэтому мгновенное включение кремниевого полевого транзистора не обязательно приведет к появлению внешнего тока стока. Для повышения помехоустойчивости транзистора можно использовать схему управления затвором, создающую небольшое отрицательное напряжение смещения, например такую, как показано на рисунке 14. Однако в оценочных платах производства компании Transphorm отрицательное смещение затвора не используется, при этом в процессе работы не наблюдается экстремально больших коммутационных потерь, обусловленных ложным включением нижнего транзистора полумостовой схемы.

Осциллограммы на рисунке 13 показывают, что при изменении VDS_Si напряжение VGS быстро приближается к пороговому уровню, однако, так как повышение VDS_Si происходит при закрытом GaN-транзисторе, ток стока кремниевого МОП-транзистора, обусловленный увеличением VGS, должен сначала разрядить затвор GaN-транзистора до того, как через транзистор начнет протекать внешний ток. Поэтому мгновенное включение кремниевого полевого транзистора не обязательно приведет к появлению внешнего тока стока. Для повышения помехоустойчивости транзистора можно использовать схему управления затвором, создающую небольшое отрицательное напряжение смещения, например такую, как показано на рисунке 14. Однако в оценочных платах производства компании Transphorm отрицательное смещение затвора не используется, при этом в процессе работы не наблюдается экстремально больших коммутационных потерь, обусловленных ложным включением нижнего транзистора полумостовой схемы.

Охлаждение

Радиатор следует подключать к цепи заземления переменного тока. В оценочной плате, фрагмент которой показан на рисунке 8, радиатор электрически соединен с полигоном земли (отрицательным полюсом источника питания), при этом оба транзистора изолированы от радиатора. Для транзистора нижнего плеча емкость между пластиной корпуса TO220 и радиатором не критична, поскольку пластина соединена с истоком, поэтому транзистор может быть установлен непосредственно на радиатор. Однако при этом возможно протекание тока нагрузки через радиатор. Если надежное соединение между пластиной корпуса транзистора и радиатором невозможно или нежелательно – необходимо использовать изолирующую прокладку. Для транзистора верхнего плеча емкость между пластиной TO220 и радиатором будет увеличивать коммутационные потери, поэтому необходимо использовать изолирующую прокладку увеличенной толщины и/или с низкой диэлектрической проницаемостью. Данную паразитную емкость можно исключить при использовании в верхнем плече транзистора Transphorm с подключением к пластине корпуса вывода стока, например, TPh4006PD.

В оценочной плате, фрагмент которой показан на рисунке 8, радиатор электрически соединен с полигоном земли (отрицательным полюсом источника питания), при этом оба транзистора изолированы от радиатора. Для транзистора нижнего плеча емкость между пластиной корпуса TO220 и радиатором не критична, поскольку пластина соединена с истоком, поэтому транзистор может быть установлен непосредственно на радиатор. Однако при этом возможно протекание тока нагрузки через радиатор. Если надежное соединение между пластиной корпуса транзистора и радиатором невозможно или нежелательно – необходимо использовать изолирующую прокладку. Для транзистора верхнего плеча емкость между пластиной TO220 и радиатором будет увеличивать коммутационные потери, поэтому необходимо использовать изолирующую прокладку увеличенной толщины и/или с низкой диэлектрической проницаемостью. Данную паразитную емкость можно исключить при использовании в верхнем плече транзистора Transphorm с подключением к пластине корпуса вывода стока, например, TPh4006PD. Однако поскольку структура внутреннего соединения «сток-пластина» отличается от структуры соединения «исток-пластина», паразитные резонансные емкости, возникающие в полумостовой схеме, будут иметь более сложный характер.

Однако поскольку структура внутреннего соединения «сток-пластина» отличается от структуры соединения «исток-пластина», паразитные резонансные емкости, возникающие в полумостовой схеме, будут иметь более сложный характер.

Особенности управления верхним плечом моста

Вследствие высоких скоростей изменения напряжения драйвер затвора верхнего плеча должен обладать хорошей устойчивостью к синфазным помехам. Для уменьшения dI/dt целесообразно выбирать драйвер затвора с меньшим выходным током: например, хороший результат показывают драйверы с выходным током 0,5 А.

Типовая бутстрепная схема питания (схема с плавающим питанием) верхнего плеча моста содержит элементы R4, D1, C12 и C13. Емкость перехода D1 непосредственно влияет на коммутационные потери, поэтому в качестве D1 должен использоваться быстрый диод с малой емкостью перехода. Резистор R4 предназначен для ограничения тока заряда конденсатора, его величина составляет 10…15 Ом. Если для питания драйвера верхнего плеча используется изолированный DC/DC-преобразователь, его проходная емкость играет ту же роль, что и емкость перехода D1 в бутстрепной схеме. Индуктивность, включенная последовательно с этой емкостью, создаст дополнительную резонансную цепь, которая будет возбуждаться при каждом импульсе коммутации, что требует тщательной разводки этого узла на печатной плате. При использовании плавающего источника питания может оказаться полезной установка синфазного помехоподавляющего дросселя.

Преимущества решений на GaN транзисторах

Рис. 15. Зависимость тока стока ID от напряжения «сток-исток» VDS в закрытом состоянии кремниевого МОП -транзистора (CoolMOS ) и каскодного GaN-транзистора (GaN-on-Si HEMT) при температуре 175°C

В таблице 2 приведено сравнение основных параметров каскодного GaN-транзистора Transphorm и современного МОП-транзистора (Superjunction MOSFET) при использовании в качестве высоковольтных ключей в мостовой схеме. GaN-транзистор TPh4006PS имеет значительно меньший заряд «затвор-исток» QGD, что обеспечивает более быструю коммутацию и, соответственно, значительно меньшие коммутационные потери по сравнению с кремниевым МОП-транзистором. При этом полный заряд затвора QG GaN-транзистора также значительно меньше, что позволяет использовать для его управления драйверы затвора с меньшим выходным током.

Графики на рисунке 15 характеризуют способность 600-вольтовых транзисторных ключей работать при высоких температурах корпуса транзистора, характерных для современной преобразовательной техники. При температуре 175°C ток стока ID кремниевого МОП-транзистора (CoolMOS) быстро растет при приближении напряжения «сток-исток» VDS в закрытом состоянии к максимальному значению 600 В, в то время как ток стока каскодного GaN-транзистора (GaN-on-Si HEMT) растет сравнительно медленно до напряжения примерно в 1 кВ, значительно превышающего рабочее напряжение.

Таблица 2. Сравнительные характеристики каскодного CaN-транзистора TPh4006PS и МОП-транзистора серии Superjunction MOSFET

| Параметр | Обозначение | Наименование | |

| Superjunction MOSFET | TPh4006PS | ||

| Максимальное напряжение «сток-исток» при температуре 25°C, В | VDS (25°C) | 600 | 600 |

| Сопротивление канала при температуре 25°C, Ом | RDS(on) (25°C) | 0,14…0,16 | 0,15…0,18 |

| Полный заряд затвора, нКл | QG | 75 | 6,2 |

| Заряд «затвор-сток», нКл | QGD | 38 | 2,2 |

| Эффективная выходная емкость, определяемая по энергии, накопленной при изменении VDS от 0 до 480 В, пФ | Co(er) | 66 | 56 |

| Эффективная выходная емкость, определяемая по времени заряда при изменении VDS от 0 до 480 В, пФ | Co(tr) | 314 | 110 |

| Заряд обратного восстановления внутреннего диода, нКл | QRR | 82001 | 542 |

| Время обратного восстановления внутреннего диода, нс | tRR | 4601 | 302 |

| Примечания: 1 – VDS = 400 В, IDS = 11,3 А, di/dt = 100 А/мкс; 2 – VDS = 480 В, IDS = 9 А, di/dt = 450 А/мкс. | |||

Типовые решения Transphorm

Одним из типовых решений Transphorm является двухтактный безмостовой корректор коэффициента мощности (ККМ), выполненный по схеме повышающего преобразователя напряжения (рисунок 16) со следующими характеристиками:

- диапазон входного переменного напряжения 85…265 В;

- выходное постоянное напряжение 387 ±5 В;

- максимальная мощность нагрузки 4400 Вт;

- частота коммутации 66 кГц.

Рис. 16. Двухтактный безмостовой ККМ с коммутатором сетевого напряжения: а) на диодах; б) на МОП-транзисторах

Рис. 17. Сигналы управления затворами SD1 и SD2

ККМ работает в режиме непрерывных токов дросселя (CCM), что оказалось возможным благодаря низким коммутационным потерям и малому времени обратного восстановления, свойственным каскодным GaN-транзисторам. ККМ содержит «быстрое» плечо на каскодных GaN-транзисторах Q1 и Q2, работающее на частоте коммутации, и «медленное» плечо, коммутирующее полуволны сетевого напряжения посредством диодов D1, D2 или МОП-транзисторов SD1, SD2. При положительной полуволне напряжения сети через открытый D1 (SD1) входная линия переменного тока подключена к выходной общей шине питания. При этом Q1 выполняет функцию активного ключа повышающего преобразователя, а Q2 – синхронного выпрямителя. При отрицательной полуволне напряжения сети через открытый D2 (SD2) входная линия переменного тока подключена к выходной плюсовой шине питания, соответственно, функции Q1 и Q2 меняются местами.

Рис. 18. Графики зависимости КПД и потерь мощности от мощности нагрузки двухтактного безмостового ККМ на GaN-транзисторах при напряжении сети 85 В (бордовый), 115 В (зеленый), 180 В (красный) и 230 В (синий)

Замена диодов, коммутирующих сетевое напряжение, МОП-транзисторами позволяет снизить потери за счет меньшего падения напряжения в открытом состоянии, однако сигналы управления МОП-транзисторами должны подаваться с некоторой паузой относительно момента сигнала полярности сетевого напряжения (рисунок 17). Это обусловлено скачкообразным изменением коэффициентов заполнения импульсов коммутации Q1 и Q2 (от 0 до 100% одного ключа и от 100% до 0 – другого) при переходе сетевого напряжения через ноль. Из-за большого времени восстановления внутренних диодов SD1 и SD2 напряжение VD (рисунок 16б) не может быстро измениться от 0 до VDC или от VDC до 0, вследствие чего в этой цепи возникает бросок тока. Для мягкого переключения с одной полуволны на другую в управление затворами SD1 и SD2 вводятся паузы, составляющие несколько периодов коммутации, в течение которых оба ключа SD1 и SD2 закрыты и работают их внутренние диоды. Кроме того, поскольку ККМ работает в режиме непрерывных токов, сравнительно большая индуктивность входного дросселя ограничивает амплитуду бросков тока. Результаты измерения КПД двухтактного безмостового ККМ (рисунок 18) показывают максимальное значение 99% при напряжении сети 230 В и мощности нагрузки 1500 Вт.

Рис. 19. Структурная схема инвертора (преобразователя постоянного напряжения в переменное) мощностью 4,5 кВт

Рис. 20. Зависимость КПД инвертора от мощности нагрузки

Другим примером типовых решений Transphorm является инвертор (рисунок 19) со следующими характеристиками:

- входное напряжение питания 400 В;

- выходное однофазное переменное напряжение 240 В, 50/60 Гц;

- частота коммутации 50 кГц.

Максимальный КПД инвертора составляет 99% при мощности нагрузки 1…2 кВт (рисунок 20).

Заключение

В силовой преобразовательной технике некоторые перспективные топологии, основные на использовании мостовых схем с жесткой коммутацией, длительное время не получали развития из-за отсутствия подходящей элементной базы. Это обусловлено тем, что к силовым ключам, особенно в высоковольтных применениях, предъявлялись требования, считавшиеся ранее несовместимыми – малое сопротивление ключа в открытом состоянии для снижения потерь проводимости и малое время переключения для снижения коммутационных потерь. Для наиболее массовых п/п-ключей – кремниевых МОП-транзисторов – ограничивающим фактором является малая ширина запрещенной зоны кремния, вследствие чего высоковольтные ключи на основе МОП-транзисторов имеют либо большое сопротивление канала в открытом состоянии, либо большую емкость затвора. Таким образом, кремниевая технология производства высоковольтных ключей практически исчерпала возможности по снижению одновременно и кондуктивных, и коммутационных потерь.

Компания Transphorm, анонсировав революционную технологию производства нитрид-галлиевых транзисторов на подложке из кремния, смогла решить большую часть проблем, связанных с производством высоковольтных ключей. Большая ширина запрещенной зоны у нитрида галлия позволяет создавать высоковольтные ключи с малым сопротивлением в открытом состоянии, а каскодная схема, состоящая из высоковольтного GaN-транзистора и низковольтного МОП-транзистора, позволила значительно уменьшить емкость затвора и время обратного восстановления внутреннего диода. Преимущества каскодных GaN-транзисторов производства компании Transphorm наглядно демонстрирует корректор коэффициента мощности на основе полумостовой схемы с жесткой коммутацией, обеспечивающий КПД 99% при мощности нагрузки 1,5 кВт. Фактически, технология производства каскодных GaN-транзисторов компании Transphorm открывает новые направления в схемотехнике силовых преобразовательных устройств – сетевых источников питания, инверторов и драйверов электродвигателей.

Таблица 1. Сравнительные характеристики различных технологий производства силовых п/п-ключей

| Наименование параметра | Технология производства силовых п/п ключей | ||

| Si | 4H-SiC | GaN | |

| Максимальная напряженность электрического поля, 106 В/см | 3 | 30 | 30 |

| Подвижность носителей заряда, см2/В•с | 1500 | 700 | 2000 |

| Коэффициент теплопроводности, Вт/см•К | 1,5 | 4,5 | 1,5 |

Таблица 2. Сравнительные характеристики каскодного CaN-транзистора TPh4006PSи МОП-транзистора серии Superjunction MOSFET

| Параметр | Обозначение | Наименование | |

| Superjunction MOSFET | TPh4006PS | ||

| Максимальное напряжение «сток-исток» при температуре 25°C, В | VDS (25°C) | 600 | 600 |

| Сопротивление канала при температуре 25°C, Ом | RDS(on) (25°C) | 0,14…0,16 | 0,15…0,18 |

| Полный заряд затвора, нКл | QG | 75 | 6,2 |

| Заряд «затвор-сток», нКл | QGD | 38 | 2,2 |

| Эффективная выходная емкость, определяемая по энергии, накопленной при изменении VDS от 0 до 480 В, пФ | Co(er) | 66 | 56 |

| Эффективная выходная емкость, определяемая по времени заряда при изменении VDS от 0 до 480 В, пФ | Co(tr) | 314 | 110 |

| Заряд обратного восстановления внутреннего диода, нКл | QRR | 82001 | 542 |

| Время обратного восстановления внутреннего диода, нс | tRR | 4601 | 302 |

| Примечания: 1 – VDS = 400 В, IDS = 11,3 А, di/dt = 100 А/мкс; 2 – VDS = 480 В, IDS = 9 А, di/dt = 450 А/мкс. | |||

•••

Наши информационные каналы

Что такое полевой транзистор и как его проверить

Добрый день, друзья!

Недавно мы с вами начали плотнее знакомились с тем, как устроено компьютерное «железо». И познакомились одним из его «кирпичиков» — полупроводниковым диодом. Компьютер – это сложная система, состоящая из отдельных частей. Разбирая, как работают эти отдельные части (большие и малые), мы приобретаем знание.

Обретая знание, мы получаем шанс помочь своему железному другу-компьютеру, если он вдруг забарахлит. Мы же ведь в ответе за тех, кого приручили, не правда ли?

Сегодня мы продолжим это интересное дело, и попробуем разобраться, как работает самый, пожалуй, главный «кирпичик» электроники – транзистор. Из всех видов транзисторов (их немало) мы ограничимся сейчас рассмотрением работы полевых транзисторов.

Почему транзистор – полевой?

Слово «транзистор» образовано от двух английских слов translate и resistor, то есть, иными словами, это преобразователь сопротивления.

Среди всего многообразия транзисторов есть и полевые, т.е. такие, которые управляются электрическим полем.

Электрическое поле создается напряжением. Таким образом, полевой транзистор – это полупроводниковый прибор, управляемый напряжением.

В англоязычной литературе используется термин MOSFET (MOS Field Effect Transistor). Есть другие типы полупроводниковых транзисторов, в частности, биполярные, которые управляются током. При этом на управление затрачивается и некоторая мощность, так как к входным электродам необходимо прикладывать некоторое напряжение.

Канал полевого транзистора может быть открыт только напряжением, без протекания тока через входные электроды (за исключением очень небольшого тока утечки). Т.е. мощность на управление не затрачивается. На практике, однако, полевые транзисторы используются большей частью не в статическом режиме, а переключаются с некоторой частотой.

Конструкция полевого транзистора обуславливает наличие в нем внутренней переходной емкости, через которую при переключении протекает некоторый ток, зависящий от частоты (чем больше частота, тем больше ток). Так что, строго говоря, некоторая мощность на управление все-таки затрачивается.

Где используются полевые транзисторы?

Настоящий уровень технологии позволяет сделать сопротивление открытого канала мощного полевого транзистора (ПТ) достаточно малым – в несколько сотых или тысячных долей Ома!

И это является большим преимуществом, так как при протекании тока даже в десяток ампер рассеиваемая на ПТ мощность не превысит десятых или сотых долей Ватта.

Таким образом, можно отказаться от громоздких радиаторов или сильно уменьшить их размеры.

ПТ широко используются в компьютерных блоках питания и низковольтных импульсных стабилизаторах на материнской плате компьютера.

Из всего многообразия типов ПТ для этих целей используются ПТ с индуцированным каналом.

Как работает полевой транзистор?

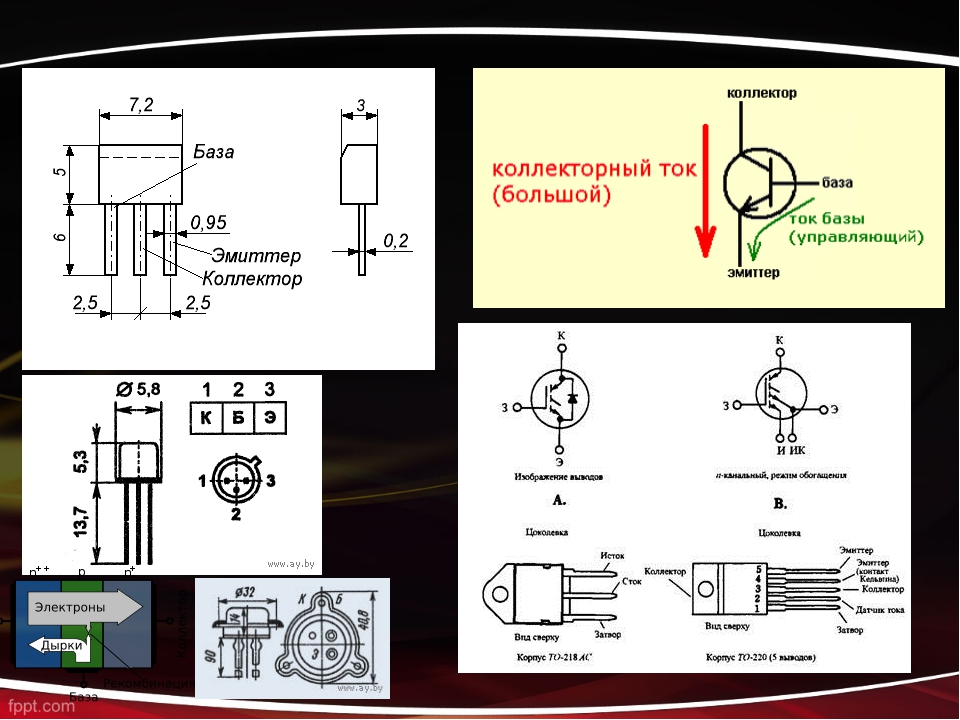

ПТ с индуцированным каналом содержит три электрода — исток (source), сток (drain), и затвор (gate).

Принцип работы ПТ наполовину понятен из графического обозначения и названия электродов.

Канал ПТ – это «водяная труба», в которую втекает «вода» (поток заряженных частиц, образующих электрический ток) через «источник» (исток).

«Вода» вытекает из другого конца «трубы» через «слив» (сток). Затвор – это «кран», который открывает или перекрывает поток. Чтобы «вода» пошла по «трубе», надо создать в ней «давление», т.е. приложить напряжение между стоком и истоком.

Если напряжение не приложено («давления в системе нет»), тока в канале не будет.

Если приложено напряжение, то «открыть кран» можно подачей напряжения на затвор относительно истока.

Чем большее подано напряжение, тем сильнее открыт «кран», больше ток в канале «сток-исток» и меньше сопротивление канала.

В источниках питания ПТ используется в ключевом режиме, т.е. канал или полностью открыт, или полностью закрыт.

Честно сказать, принципы действия ПТ гораздо более сложны, он может работать не только в ключевом режиме. Его работа описывается многими заумными формулами, но мы не будем здесь все это описывать, а ограничимся этими простыми аналогиями.

Скажем только, что ПТ могут быть с n-каналом (при этом ток в канале создается отрицательно заряженными частицами) и p-каналом (ток создается положительно заряженными частицами). На графическом изображении у ПТ с n-каналом стрелка направлена внутрь, у ПТ с p-каналом – наружу.

Собственно, «труба» — это кусочек полупроводника (чаще всего – кремния) с примесями химических элементов различного типа, что обуславливает наличие положительных или отрицательных зарядов в канале.

Теперь переходим к практике и поговорим о том,

Как проверить полевой транзистор?

В норме сопротивление между любыми выводами ПТ бесконечно велико.

И, если тестер показывает какое-то небольшое сопротивление, то ПТ, скорее всего, пробит и подлежит замене.

Во многих ПТ имеется встроенный диод между стоком и истоком для защиты канала от обратного напряжения (напряжения обратной полярности).

Таким образом, если поставить «+» тестера (красный щуп, соединенный с «красным» входом тестера) на исток, а «-» (черный щуп, соединенный с черным входом тестера) на сток, то канал будет «звониться», как обычный диод в прямом направлении.

Это справедливо для ПТ с n-каналом. Для ПТ с p-каналом полярность щупов будет обратной.

Как проверить диод с помощью цифрового тестера, описано в соответствующей статье. Т.е. на участке «сток — исток» будет падать напряжение 500-600 мВ.

Если поменять полярность щупов, к диоду будет приложено обратное напряжение, он будет закрыт и тестер это зафиксирует.

Однако исправность защитного диода еще не говорит об исправности транзистора в целом. Более того, если «прозванивать» ПТ, не выпаивая из схемы, то из-за параллельно подключенных цепей не всегда можно сделать однозначный вывод даже об исправности защитного диода.

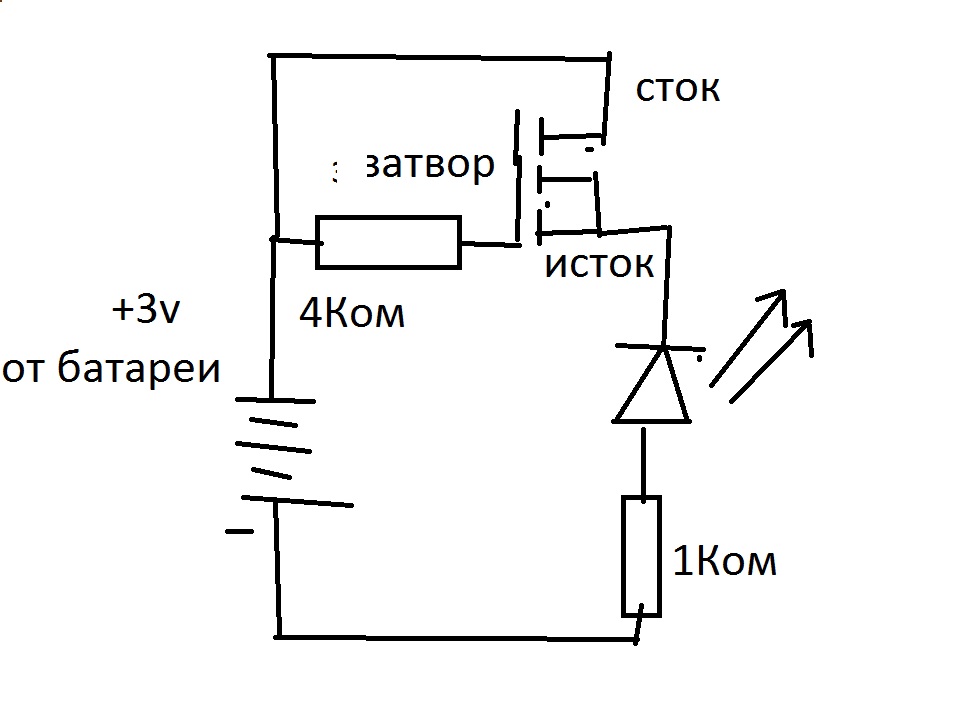

В таких случаях можно выпаять транзистор, и, используя небольшую схему для тестирования, однозначно ответить на вопрос – исправен ли ПТ или нет.

В исходном состоянии кнопка S1 разомкнута, напряжение на затворе относительно стока равно нулю. ПТ закрыт, и светодиод HL1 не светится.

При замыкании кнопки на резисторе R3 появляется падение напряжения (около 4 В), приложенное между истоком и затвором. ПТ открывается, и светодиод HL1 светится.

Эту схему можно собрать в виде модуля с разъемом для ПТ. Транзисторы в корпусе D2 pack (который предназначен для монтажа на печатную плату) в разъем не вставишь, но можно припаять к его электродам проводники, и уже их вставить в разъем. Для проверки ПТ с p-каналом полярность питания и светодиода нужно изменить на обратную.

Иногда полупроводниковые приборы выходят из строя бурно, с пиротехническими, дымовыми и световыми эффектами.

В этом случае на корпусе образуются дыры, он трескается или разлетается на куски. И можно сделать однозначный вывод об их неисправности, не прибегая к приборам.

В заключение скажем, что буквы MOS в аббревиатуре MOSFET расшифровываются как Metal — Oxide — Semiconductor (металл – оксид – полупроводник). Такова структура ПТ – металлический затвор («кран») отделен от канала из полупроводника слоем диэлектрика (оксида кремния).

Надеюсь, с «трубами», «кранами» и прочей «сантехникой» вы сегодня разобрались.

Однако, теория, как известно, без практики мертва! Надо обязательно поэкспериментировать с полевиками, поковыряться, повозиться с их проверкой, пощупать, так сказать.

Что вызывает это колено в моем падении напряжения стока МОП-транзистора?

Наклон напряжения стока зависит от емкости затвора-стока Cgd. В случае падения фронта транзистор должен разрядить Cgd. В дополнение к току нагрузки для резистора он также должен поглощать ток, протекающий через Cgd.

Важно помнить, что Cgd — это не простой конденсатор, а нелинейная емкость, которая зависит от рабочей точки. В насыщении нет канала на стороне стока транзистора, и Cgd происходит из-за емкости перекрытия между затвором и стоком. В линейной области канал простирается в сторону стока, и Cgd больше, потому что теперь между затвором и стоком имеется большая емкость затвора для канала.

Когда транзистор переходит между насыщением и линейной областью, значение Cgd изменяется и, следовательно, также наклон напряжения стока.

Использование LTspice Cgd можно проверить с помощью симуляции «Рабочая точка постоянного тока». Результаты можно просмотреть с помощью «Просмотр / Spice Error Log».

Для Vgs 3,92 В Cgd составляет около 1,3 нПФ, потому что Vds высокое.

Name: m1

Model: irf2805s

Id: 1.70e-02

Vgs: 3.92e+00

Vds: 6.60e+00

Vth: 3.90e+00

Gm: 1.70e+00

Gds: 0.00e+00

Cgs: 6.00e-09

Cgd: 1.29e-09

Cbody: 1.16e-09

Для Vgs 4 В Cgd намного больше с 6,5 нФ из-за более низких Vds.

Name: m1

Model: irf2805s

Id: 5.00e-02

Vgs: 4.00e+00

Vds: 6.16e-03

Vth: 3.90e+00

Gm: 5.15e-01

Gds: 7.98e+00

Cgs: 6.00e-09

Cgd: 6.52e-09

Cbody: 3.19e-09

Изменение Cgd (обозначенное Crss) для разных смещений можно увидеть на графике ниже, взятом из таблицы данных.

IRF2805 — это транзистор VDMOS, который показывает другое поведение для Cgd. Из интернета :

Дискретный вертикальный MOSFET-транзистор с двойным рассеиванием (VDMOS), широко используемый в источниках питания с переключателем уровня платы, имеет поведение, качественно отличающееся от описанных выше монолитных моделей MOSFET. В частности, (i) диод корпуса транзистора VDMOS подключен к внешним клеммам иначе, чем диод подложки монолитного полевого МОП-транзистора, и (ii) нелинейность ёмкости затвор-сток (Cgd) не может быть смоделирована с помощью простой градуировки Емкости монолитных моделей MOSFET. В транзисторе VDMOS Cgd резко изменяется примерно на нулевое напряжение затвора (Vgd). Когда Vgd отрицателен, Cgd физически основан на конденсаторе с затвором в качестве одного электрода и стоком на задней стороне матрицы в качестве другого электрода. Эта емкость довольно низкая из-за толщины непроводящего кристалла. Но когда Vgd положительный, матрица является проводящей, а Cgd физически основан на конденсаторе с толщиной оксида затвора. Традиционно, сложные подсхемы использовались, чтобы дублировать поведение мощного MOSFET. Было написано новое встроенное устройство специй, которое воплощает это поведение в интересах скорости вычислений, надежности сходимости и простоты написания моделей. Модель DC аналогична монолитному MOSFET уровня 1, за исключением того, что длина и ширина по умолчанию равны единице, так что коэффициент трансдуктивности может быть задан напрямую без масштабирования. Модель переменного тока выглядит следующим образом. Емкость затвор-источник принимается постоянной. Опытным путем было установлено, что это хорошее приближение для мощных полевых МОП-транзисторов, если напряжение затвор-исток не приводится в действие отрицательным. Емкость затвор-сток принимает следующую эмпирически найденную форму:

Для положительного Vgd Cgd изменяется как гиперболический тангенс Vgd. Для отрицательного Vdg Cgd изменяется как арктангенс Vgd. Параметры модели a, Cgdmax и Cgdmax параметризуют емкость стока затвора. Емкость исток-сток поступает через градуированную емкость диода корпуса, подключенного к электродам стока истока, вне сопротивлений истока и истока.

В файле модели можно найти следующие значения

Cgdmax=6.52n Cgdmin=.45n

Очень прерывистый сбой питания МОП-транзистора

Я работаю на очень пятнистый отказ двигателя (я не дизайнер). У нас есть намотанная арматура, которая переключается с помощью силовых полевых МОП-транзисторов. Они приводятся в действие FET драйвером типа тотема. Следовательно, когда драйвер выключен, затвор силового полевого транзистора плавает. Да, я знаю. Плохой дизайнерский выбор. Я просто убираю беспорядок.

На стороне статора двигателя имеется цепь симистора и привода, управляемая микропроцессором. Когда вы подключаете двигатель, приводная линия остается на плаву, поскольку микропорт переключается до завершения загрузки. Поскольку эта линия порта входит в логический элемент И и находится в плавающем состоянии, в результате получается около 5 циклов переменного тока с достаточной амплитудой для срабатывания вентиля, а это — симистор. Это помещает примерно 3-5 полупериодов линии на статор, с пиками до 100 А в зависимости от полного сопротивления источника. Ага. Еще одна ошибка дизайна — его надо было снести.

Проблема — это случается не часто, и не происходит сбой питания MOSFET. Из сотен двигателей у нас было три выхода из строя с мощными полевыми транзисторами, замкнутыми стоком и затвором в источник. Вопрос — я пытаюсь решить, является ли эта серия пиков тока (которые вызывают напряжение на якоре — и отношение витков составляет 1: 1) вероятным подозрением, учитывая плохо спроектированную схему силового полевого МОП-транзистора. МОП-транзисторы расположены прямо через обмотку якоря. Когда двигатель выходит из строя, он не выходит из строя во время работы. Похоже, что он потерпит неудачу, как только вы подключите его. Все мои доказательства косвенные — я до сих пор не смог вызвать неудачу. Но огромный всплеск на плагине, редкость неудачи и трудность дублирования, похоже, указывают на это. Если я иду по неверному пути, мне нужно знать и знать почему. Кажется, что это может повредить FET, но я ищу путь к неудаче, который имеет смысл.

В данный момент я запускаю несколько двигателей, используя ПЛК, чтобы следить за ними. План состоит в том, чтобы выполнить цикл до отказа, применить исправления проекта и запустить снова. Если я не получу вспышку гения.

Рассел МакМахон

Ворота FET НЕ ДОЛЖНЫ плавать.

Ничто не может быть гарантировано в этом состоянии.

Емкость Миллера будет успешно соединять большие сигналы привода на затворе от переходных процессов стока. Затвор, управляемый выше его значения Vgsmax, будет достаточно часто прокалывать оксид затвора, и может возникнуть любая комбинация жестких шортов между GDS. Я видел DS коротким с открытым G, GS коротким с открытым D, GDS коротким и, возможно, GD коротким с открытым S, но я не был бы уверен на 100% в этом.

Для ЛЮБОГО мощного полевого транзистора с индуктивной нагрузкой я добавляю стабилитрон GS, установленный как можно ближе к полевому транзистору, с номинальным напряжением выше Vgs_drive_max и комфортно ниже VGS_abs_max. Это преобразует цепи, которые выходят из строя в считанные минуты или часы, в цепи, которые никогда не выходят из строя.

Buz90 datasheet на русском

| Главная | О сайте | Теория | Практика | Контакты |

Высказывания: Основные параметры BUZ90A полевого транзистора n-канального.Эта страница показывает существующую справочную информацию о параметрах полевого транзистора n-канального BUZ90A. Дана подробная информация о параметрах, схеме и цоколевке, характеристиках, местах продажи и производителях. Структура (технология): MOSFET |

| Pd max | Uds max | Udg max | Ugs max | Id max | Tj max, °C | Fr (Ton/of) | Ciss tip | Rds |

| 75W | 600V | 600V | ±20V | 4A | 150°C | 30/150nS | 1050pF | 2 |

Производитель: SIEMENS

Сфера применения: SIPMOS Power V-MOS

Популярность: 6452

Условные обозначения описаны на странице «Теория».

Схемы транзистора BUZ90A

| Общий вид транзистора BUZ90A. | Цоколевка транзистора BUZ90A. |

Обозначение контактов:

Международное: G – затвор, D – сток, S – исток.

Российское: З – затвор, С – сток, И – исток.

Коллективный разум. Дополнения для транзистора BUZ90A.

Другие разделы справочника:

Есть надежда, что справочник транзисторов окажется полезен опытным и начинающим радиолюбителям, конструкторам и учащимся. Всем тем, кто так или иначе сталкивается с необходимостью узнать больше о параметрах транзисторов. Более подробную информацию обо всех возможностях этого интернет-справочника можно прочитать на странице «О сайте».

Если Вы заметили ошибку, огромная просьба написать письмо.

Спасибо за терпение и сотрудничество.

BUZ90 MOSFET – описание производителя. Даташиты. Основные параметры и характеристики. Поиск аналога. Справочник

Наименование прибора: BUZ90

Тип транзистора: MOSFET

Максимальная рассеиваемая мощность (Pd): 75 W

Предельно допустимое напряжение сток-исток (Uds): 600 V

Предельно допустимое напряжение затвор-исток (Ugs): 20 V

Максимально допустимый постоянный ток стока (Id): 4.5 A

Максимальная температура канала (Tj): 150 °C

Выходная емкость (Cd): 1050 pf

Сопротивление сток-исток открытого транзистора (Rds): 1.6 Ohm

Тип корпуса: TO220AB

BUZ90 Datasheet (PDF)

1.1. buz90a.pdf Size:175K _siemens

BUZ 90 A SIPMOS � Power Transistor � N channel � Enhancement mode � Avalanche-rated Pin 1 Pin 2 Pin 3 G D S Type VDS >1.2. buz90.pdf Size:176K _siemens

BUZ 90 SIPMOS � Power Transistor � N channel � Enhancement mode � Avalanche-rated Pin 1 Pin 2 Pin 3 G D S Type VDS >

BUZ900DP MAGNA BUZ901DP TEC MECHANICAL DATA Dimensions in mm N�CHANNEL POWER MOSFET 20.0 5.0 3.3 Dia. POWER MOSFETS FOR AUDIO APPLICATIONS FEATURES 1 2 3 � HIGH SPEED SWITCHING 2.0 1.0 � N�CHANNEL POWER MOSFET 2.0 � SEMEFAB DESIGNED AND DIFFUSED 3.4 � HIGH VOLTAGE (160V & 200V) � HIGH ENERGY RATING 0.6 1.2 � ENHANCEMENT MODE 2.8 � INTEGRAL PROTECTION DIODE 5.45 5.45 � P�

BUZ900D MAGNA BUZ901D TEC MECHANICAL DATA Dimensions in mm N–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • N–CHANNEL POWER MOSFET • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (160V & 200V) R 4.0 ± 0.1 R 4.4 ± 0.2 • HIGH ENERGY RATING • ENHANC

BUZ900P MAGNA BUZ901P TEC MECHANICAL DATA Dimensions in mm (inches) N–CHANNEL POWER MOSFET 4.69 (0.185) 15.49 (0.610) 5.31 (0.209) 16.26 (0.640) 1.49 (0.059) 2.49 (0.098) POWER MOSFETS FOR AUDIO APPLICATIONS 3.55 (0.140) 3.81 (0.150) FEATURES 1 2 3 • HIGH SPEED SWITCHING 1.65 (0.065) 2.13 (0.084) 0.40 (0.016) • N–CHANNEL POWER MOSFET 0.79 (0.031) 2.87 (0.113) 3.1

BUZ907D MAGNA BUZ908D TEC MECHANICAL DATA Dimensions in mm P–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (220V & 250V) • HIGH ENERGY RATING R 4.0 ± 0.1 R 4.4 ± 0.2 • ENHANCEMENT MODE • INTEGRAL PROT

BUZ900 www.DataSheet4U.com MAGNA BUZ901 TEC MECHANICAL DATA Dimensions in mm N–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • N–CHANNEL POWER MOSFET • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (160V & 200V) R 4.0 ± 0.1 R 4.4 ± 0.2 • HIGH ENERGY

BUZ907P MAGNA BUZ908P TEC MECHANICAL DATA Dimensions in mm P–CHANNEL 4.69 (0.185) 15.49 (0.610) POWER MOSFET 5.31 (0.209) 16.26 (0.640) 1.49 (0.059) 2.49 (0.098) POWER MOSFETS FOR AUDIO APPLICATIONS 3.55 (0.140) 3.81 (0.150) FEATURES 1 2 3 • HIGH SPEED SWITCHING 1.65 (0.065) 2.13 (0.084) 0.40 (0.016) • SEMEFAB DESIGNED AND DIFFUSED 0.79 (0.031) 2.87 (0.113) 3.12 (0

BUZ905X4S MAGNA BUZ906X4S TEC NEW PRODUCT UNDER DEVELOPMENT MECHANICAL DATA Dimensions in mm (inches) P–CHANNEL POWER MOSFET 11.8 (0.463) 12.2 (0.480) 31.5 (1.240) 31.7 (1.248) POWER MOSFETS FOR 8.9 (0.350) 7.8 (0.307) 4.1 (0.161 ) 8.2 (0.322) W = 9.6 (0.378) Hex Nut M 4 4.3 (0.169 ) (4 places) AUDIO APPLICATIONS 4.8 (0.187) H = 4.9 (0.193) 1 2 (4 places) R 4.0 (0.

BUZ902 MAGNA BUZ903 TEC MECHANICAL DATA Dimensions in mm N–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (220V & 250V) • HIGH ENERGY RATING R 4.0 ± 0.1 R 4.4 ± 0.2 • ENHANCEMENT MODE • INTEGRAL PROTEC

BUZ902D MAGNA BUZ903D TEC MECHANICAL DATA Dimensions in mm N–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (220V & 250V) • HIGH ENERGY RATING R 4.0 ± 0.1 R 4.4 ± 0.2 • ENHANCEMENT MODE • INTEGRAL PROT

BUZ905DP MAGNA BUZ906DP TEC MECHANICAL DATA Dimensions in mm P–CHANNEL POWER MOSFET 20.0 5.0 3.3 Dia. POWER MOSFETS FOR AUDIO APPLICATIONS FEATURES 1 2 3 • HIGH SPEED SWITCHING 2.0 1.0 • P–CHANNEL POWER MOSFET 2.0 • SEMEFAB DESIGNED AND DIFFUSED 3.4 • HIGH VOLTAGE (160V & 200V) • HIGH ENERGY RATING 0.6 1.2 • ENHANCEMENT MODE 2.8 • INTEGRAL PROTECTION D

BUZ905D MAGNA BUZ906D TEC MECHANICAL DATA Dimensions in mm P–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • P–CHANNEL POWER MOSFET • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (160V & 200V) R 4.0 ± 0.1 R 4.4 ± 0.2 • HIGH ENERGY RATING • ENHANC

BUZ907DP MAGNA BUZ908DP TEC MECHANICAL DATA Dimensions in mm P–CHANNEL POWER MOSFET 20.0 5.0 3.3 Dia. POWER MOSFETS FOR AUDIO APPLICATIONS FEATURES 1 2 3 • HIGH SPEED SWITCHING 2.0 1.0 2.0 • SEMEFAB DESIGNED AND DIFFUSED 3.4 • HIGH VOLTAGE (220V & 250V) • HIGH ENERGY RATING 0.6 1.2 • ENHANCEMENT MODE 2.8 • INTEGRAL PROTECTION DIODES 5.45 5.45 • COMPLI

BUZ907 MAGNA BUZ908 TEC MECHANICAL DATA Dimensions in mm P�CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 � 0.1 1.50 11.60 POWER MOSFETS FOR Typ. � 0.3 AUDIO APPLICATIONS FEATURES 1 2 � HIGH SPEED SWITCHING � SEMEFAB DESIGNED AND DIFFUSED � HIGH VOLTAGE (220V & 250V) � HIGH ENERGY RATING R 4.0 � 0.1 R 4.4 � 0.2 � ENHANCEMENT MODE � INTEGRAL PROTECTION DIODES � COMPLI

BUZ905P MAGNA BUZ906P TEC MECHANICAL DATA Dimensions in mm (inches) P–CHANNEL POWER MOSFET 4.69 (0.185) 15.49 (0.610) 5.31 (0.209) 16.26 (0.640) 1.49 (0.059) 2.49 (0.098) POWER MOSFETS FOR AUDIO APPLICATIONS 3.55 (0.140) 3.81 (0.150) FEATURES 1 2 3 • HIGH SPEED SWITCHING 1.65 (0.065) 2.13 (0.084) 0.40 (0.016) • P–CHANNEL POWER MOSFET 0.79 (0.031) 2.87 (0.113) 3.1

BUZ902DP MAGNA BUZ903DP TEC MECHANICAL DATA Dimensions in mm N–CHANNEL POWER MOSFET 20.0 5.0 3.3 Dia. POWER MOSFETS FOR AUDIO APPLICATIONS FEATURES 1 2 3 • HIGH SPEED SWITCHING 2.0 1.0 2.0 • SEMEFAB DESIGNED AND DIFFUSED 3.4 • HIGH VOLTAGE (220V & 250V) • HIGH ENERGY RATING 0.6 1.2 • ENHANCEMENT MODE 2.8 • INTEGRAL PROTECTION DIODES 5.45 5.45 • COMPLI

BUZ902P MAGNA BUZ903P TEC MECHANICAL DATA Dimensions in mm N�CHANNEL 4.69 (0.185) 15.49 (0.610) POWER MOSFET 5.31 (0.209) 16.26 (0.640) 1.49 (0.059) 2.49 (0.098) POWER MOSFETS FOR AUDIO APPLICATIONS 3.55 (0.140) 3.81 (0.150) FEATURES 1 2 3 � HIGH SPEED SWITCHING 1.65 (0.065) 2.13 (0.084) 0.40 (0.016) � SEMEFAB DESIGNED AND DIFFUSED 0.79 (0.031) 2.87 (0.113) 3.12 (0.123) �

BUZ900X4S MAGNA BUZ901X4S TEC NEW PRODUCT UNDER DEVELOPMENT MECHANICAL DATA Dimensions in mm (inches) N–CHANNEL POWER MOSFET 11.8 (0.463) 12.2 (0.480) 31.5 (1.240) 31.7 (1.248) POWER MOSFETS FOR 8.9 (0.350) 7.8 (0.307) 4.1 (0.161 ) 8.2 (0.322) W = 9.6 (0.378) Hex Nut M 4 4.3 (0.169 ) (4 places) AUDIO APPLICATIONS 4.8 (0.187) H = 4.9 (0.193) 1 2 (4 places) R 4.0 (0.

1.20. buz905-06.pdf Size:40K _magnatec

BUZ905 MAGNA BUZ906 TEC MECHANICAL DATA Dimensions in mm P–CHANNEL POWER MOSFET +0.1 25.0 -0.15 8.7 Max. 10.90 ± 0.1 1.50 11.60 POWER MOSFETS FOR Typ. ± 0.3 AUDIO APPLICATIONS FEATURES 1 2 • HIGH SPEED SWITCHING • P–CHANNEL POWER MOSFET • SEMEFAB DESIGNED AND DIFFUSED • HIGH VOLTAGE (160V & 200V) R 4.0 ± 0.1 R 4.4 ± 0.2 • HIGH ENERGY RATING • ENHANCEM

BUZ90 (Siemens Semiconductor Group)

Power Transistor

No Preview Available !

Click to Download PDF File for PC

BUZ90 (Siemens Semiconductor Group)

Power Transistor

No Preview Available !

Характеристики полевых транзисторов. OrCAD PSpice. Анализ электрических цепей

Характеристики полевых транзисторов

Демонстрационная версия OrCAD имеет компоненты J2N3819 и J2N4393 в качестве моделей для полевых n-канальных транзисторов (JFET). Чтобы получить семейство выходных характеристик, создайте новый проект с именем Jfetch. Используем простую схему (рис. 15.22). Номинальные значения для VGS и VDD показаны на рисунке. Определите опции моделирования в Simulation Profile, используя имя jfetchs. Внутренний цикл вариации использует значения источника напряжения VDD от 0 до 12 В с шагом в 0,2 В. Внешний цикл определяется изменением напряжения VGS от 0 до 4 В с шагом в 1 В.

Рис. 15.22. Схема смещения для n-канального полевого транзистора

Выполните моделирование и получите в Probe график ID(J1). Вы должны получить семейство кривых с параметром VGS, приведенных на рис. 15.23. Кривые показывают, что наибольшие токи соответствуют VGS=0. Ниже расположена кривая с параметром VGS=–1 В и так далее. Напряжением отсечки является VGS=–3 В.

Рис. 15.23. Ток стока в n-канальном полевом транзисторе

Выходной файл включает параметры модели J2N3S19: пороговое напряжение (отсечки) VTO=-3 В, коэффициент передачи BETA и другие. Они отражены на рис. 15.24. В приложении D приведены все параметры модели для J (JFET).

**** 10/03/99 11:45:33 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: jfetchs

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.DC LIN V VDD 0V 12V 0.2V

+ LIN V_VGS 0V 4V 1V

.PROBE

*Netlist File:

.INC «jfetch-SCHEMATIC1.net»

*Alias File:

**** INCLUDING jfetch-SCHEMATIC1.net ****

* source JFETCH

J_J1 2 1 0 J2N3819

V_VDD 2 0 12V

V_VGS 0 1 1V

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir

**** .INC «jfetch-SCHEMATIC1.als»

**** INCLUDING jfetch-SCHEMATIC1.als ****

.ALIASES

J_J1 J1(d=2 g=1 s=0 )

V_VDD VDD(+=2 -=0 )

V_VGS VGS(+=0 -=1 )

_ _(1=1)

_ _(2=2)

.ENDALIASES

.END

**** Junction FET MODEL PARAMETERS

J2N3819

NJF

VTO -3

BETA 1.304000E-03

LAMBDA 2.250000E-03

IS 33.570000E-15

ISR 322.400000E-15

ALPHA 311.700000E-06

VK 243.6

RD 1

RS 1

CGD 1.600000E-12

CGS 2.414000E-12

M .3622

VTOTC -2.500000E-03

BETATCE -.5

KF 9.882000E-18

Рис. 15.24. Выходной файл для n-канального полевого транзистора

Хотя предыдущие выпуски программного обеспечения от MicroSim использовали для создания рисунков программу Schematics вместо Capture, автоматически формируя команду .ОР в схемном файле, используемая в книге версия Capture этого не делает. Следовательно, значения параметров смещения не выводятся в выходном файле. Чтобы получить эти значения, отредактируете параметры настройки моделирования и запросите анализ параметров смещения путем проверки с опцией .OP. Выходной файл при таком запуске показан на рис. 15.25. Информация, дублирующая информацию предыдущего выходного файла, из него удалена. Убедитесь, что выходной файл соответствует графику, показывая VDD=12 В, VGS=–1 В, IDD=5,328 мА.

**** 10/03/99 12:27:36 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: jfetchs

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.OP

.PROBE

*Netlist File:

.INC «jfetch-SCHEMATIC1.net»

*Alias File:

**** INCLUDING jfetch-SCHEMATIC1.net ****

* source JFETCH

J_J1 2 10 J2N3819

V_VDD 2 0 12V

V_VGS 0 1 1V

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir ****

.INC «jfetch-SCHEMATIC1.als»

**** INCLUDING jfetch-SCHEMATIC1.als ****

.ALIASES

J_J1 J1(d=2 g=1 s=0 )

V_VDD VDD(+=2 -=0)

V_VGS VGS(+=0 -=1 )

_ _(1=1)

_ _(2=2)

.ENDALIASES

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir ****

.END

**** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) -1.0000 ( 2) 12.0000

VOLTAGE SOURCE CURRENTS

NAME CURRENT

V_VDD -5.328E-03

V_VGS -1.321E-12

TOTAL POWER DISSIPATION 6.39E-02 WATTS

**** JFETS

NAME J_J1

MODEL J2N3819

ID 5.33E-03

VGS -1.00E+00

VDS 1.20E+01

GM 5.34E-03

GDS 1.17E-05

CGS 1.83E-12

CGD 6.15E-13

Рис. 15.25. Выходной файл, использующий опцию .OР

Данный текст является ознакомительным фрагментом.

Продолжение на ЛитРесРуководство для начинающих по MOSFET

IRFP260N, изображение с сайта warf.com. Пины — Gate, Drain, Source слева направо.

Если вам нужно переключать сильноточные и / или высоковольтные нагрузки с помощью микроконтроллера, вам понадобится какой-либо тип транзистора. Я собираюсь рассказать, как использовать полевой МОП-транзистор, поскольку это лучший вариант для мощных нагрузок. Это руководство будет всего лишь кратким введением, в котором будет рассказано, как управлять MOSFET простым способом с конечной целью — заставить его работать как идеальный переключатель.Я не собираюсь вдаваться в такие темы, как область триода, насыщенность, пороговое напряжение и т. Д.

Обратитесь к базовой схеме подключения N- или P-канала и запомните три контакта: Gate, Drain и Source. Когда я упоминаю что-то вроде разности потенциалов затвор-исток, я имею в виду разницу в напряжении между двумя контактами.

Спасибо Farnell.com за поставку многих деталей, которые будут частью этого обзора / руководства. Я также хотел бы отметить, что все части работают отлично!

N-канальный полевой МОП-транзистор

Как думать о полевом МОП-транзисторе:

МОП-транзистор можно рассматривать как переменный резистор, сопротивление сток-исток которого (обычно Rds) является функцией разности напряжений на выводах затвор-исток.Если нет разницы потенциалов между затвором-источником, тогда сопротивление сток-исток очень велико и его можно рассматривать как разомкнутый переключатель, поэтому ток не может течь через контакты сток-исток. Когда существует большая разность потенциалов затвор-исток, сопротивление сток-исток очень низкое и его можно рассматривать как замкнутый переключатель — ток может течь через контакты сток-исток.

МОП-транзистор с каналом P

N-канал — для N-канального MOSFET источник заземлен.Если мы хотим позволить току течь, мы можем легко поднять напряжение на затворе, позволяя току течь. Если ток не должен течь, штифт затвора должен быть заземлен.

Канал P — если посмотреть на полевой МОП-транзистор с каналом P, то можно увидеть, что источник подключен к шине питания V2. Чтобы позволить току течь, ворота должны быть заземлены. Чтобы остановить прохождение тока, затвор нужно подтянуть к V2. Потенциальная проблема заключается в том, что если V2 представляет собой очень высокое напряжение, может быть трудно поднять затвор до напряжения V2.Более того, MOSFET имеет ограничения на разность потенциалов затвор-исток. Также обратите внимание, что логика инвертирована для МОП-транзистора P-типа!

Сопротивление сток-источник — в идеале мы хотим, чтобы сопротивление сток-источник было очень высоким, когда ток не течет, и очень низким, когда ток течет. Основная проблема, связанная с использованием полевых МОП-транзисторов с микроконтроллерами, заключается в том, что для МОП-транзистора может потребоваться разность потенциалов 10-15 затвор-исток, чтобы приблизиться к самому низкому сопротивлению сток-исток, но микроконтроллер может работать от 5 В или 3 В.3в. Требуется какой-то драйвер MOSFET.

IRFP260N емкость затвора

Кривые тока IRFP260N.

Емкость затвор-исток — на выводах затвор-исток также имеется емкость, которая не позволяет полевому МОП-транзистору быстро переключать состояния. Чтобы быстро изменять напряжение на внутренней емкости, драйвер MOSFET должен быть сильноточным. Он также должен активно заряжать (источник) и разряжать (сток) конденсатор (для канала N)!

Драйверы MOSFET:

Полумост способен на то, что было сказано выше! Есть много доступных микросхем, которые могут это сделать.Вот список из нескольких, которые я протестировал. Схемы также предоставляются!

Драйвер Fet — полумост

- MIC4422YN — Макс 18 В, пик 9 А, непрерывный 2 А.

- MCP1407 — Макс 18 В, 6 А в пике, 1,3 А в непрерывном режиме.

- UCC27424 — Может управлять двумя полевыми МОП-транзисторами, макс. 15 В, типичное значение 4 А.

Все эти драйверы работали примерно одинаково (подъем ~ 20 нс, спад ~ 30 нс). Обратите внимание, что, хотя они могут использоваться не только для драйверов MOSFET, эти микросхемы не обладают большой способностью рассеивать тепло!

МОП-транзисторов, которые я тестировал:

Изначально планировалось собрать данные об этих парнях, но я был очень занят школой.В таблицах данных для полевых МОП-транзисторов есть множество графиков!

Корпусный диод полевого МОП-транзистораP вызывает непреднамеренное протекание тока.

UCC27424

MIC4422YN и MCP1407

- IRFP260N — канал 200В, 50А, N.

- IRF3703PBF — 30в, 210А, канал N. Вводящие в заблуждение рейтинги! Прочтите мои примечания к таблице данных в конце.

- RFP30N06LE — канал 60в, 30А, N.

- FQP27P06– 60В, 27А, канал P.

Важное напоминание — не забывайте, что обычно радиатор на задней панели МОП подключается к сливу! Если вы устанавливаете несколько полевых МОП-транзисторов на радиатор, они должны быть электрически изолированы от радиатора! Если радиатор прикреплен к заземляющей раме болтами, рекомендуется изолировать его.

Корпусный диод— МОП-транзисторы также имеют внутренний диод, который может пропускать ток непреднамеренно (см. Пример). Внутренний диод также ограничивает скорость переключения. Это не будет проблемой, если вы работаете на частоте ниже 1 МГц.

Отличная шпаргалка, включая МОП-транзисторы. — akafugu.jp

Примечание о затворе — Напряжение источника: затворы MOSFET могут быть выше или ниже напряжения источника. Таким образом, для N-канального МОП-транзистора с источником на 0 В, -10 В на затворе позволит току течь. Проверьте это с помощью таблицы данных вашего MOSFET!

Схема диода— Если нагрузка несколько индуктивная, вам потребуется установить диод для разряда индуктивности.Если вы хотите получить более подробную информацию, посмотрите pdf-файл International Rectifier в конце. В моем «Введение в повышающий преобразователь» также рассказывается о природе индукторов при быстром включении / выключении.

Звонок от ворот-источника — Есть несколько методов, о которых я слышал / видел, чтобы ограничить звонок на воротах. Звонок снижает эффективность и, если он чрезмерен, может повредить полевой МОП-транзистор. Вы можете использовать стабилитрон и резистор последовательно с катодом стабилитрона, подключенным к затвору, анодом, подключенным к истоку для канала N. Канал P будет перевернут стабилитроном.Добавьте резистор, чтобы ограничить ток, проходящий через стабилитрон, и наблюдайте за этими пробивными напряжениями! Есть также еще один диод, который вы могли бы изучить, называемый TVS-диодом.

Примечания к техническому паспорту — Если у детали слишком хорошие, чтобы соответствовать действительности, внимательно ознакомьтесь с примечаниями к применению. Например, IRF3703PBF требует постоянного тока стока 210 А при 25ºC. Нам не нужно делать никаких тепловых расчетов, чтобы знать, что 220 А — это ТОННА тока для корпуса TO-220! При более внимательном рассмотрении на странице 8, примечание 6 видно, что он может непрерывно пропускать максимум 75 А из-за тепловых ограничений корпуса.На будущее: IRF довольно хорошо дает точные рейтинги, но вы должны искать такие вещи. Сейчас в реальном мире множество тестов показывает, плохой ли ваш дизайн, или вы работаете с нечестным или некомпетентным поставщиком с неточными / вводящими в заблуждение таблицами данных.

UCC27424, MIC4422YN, MCP1407

Пример Arduino Mosfet

Без драйвера для зарядки Gate требуется больше времени, и его пик составляет 5 В. Чрезмерный звон из-за отсутствия подавления звонка на затворе.

Большое дополнительное чтение:

Информация по применению MOSFET International Rectifier MOSFET

Руководство по высокоскоростному полевому МОП-транзистору

M: полевой МОП-транзистор

M: полевой МОП-транзисторДалее: Q: Биполярный переходный транзистор Up: Описание схемы Предыдущая: L: Индуктор & nbsp Содержание

Подразделы

M xxxxxxx nd ng ns nb mname { args }

M xxxxxxx ng ns nb mname { ширина / длина } { args }

.MOSfet label nd ng ns nb mname { args }

.MOSfet этикетка nd ng ns nb mname { ширина / длина } { args }

МОП-транзистор.

Nd , ng , ns и nb — сток, затвор, исток и объемные (субстратные) узлы соответственно. Mname — это название модели.

Длина и ширина — длина и ширина нарисованного канала, дюйм микрон.Обратите внимание, что обозначение W / L имеет единицы микрон, но то же самое параметры, в списке аргументов (W и L) указаны единицы измерения. Все остальные размеры указаны в метрах.

Параметры rstray и norstray определяют, нужно ли включены последовательные сопротивления. rstray используется по умолчанию. Опыт показал, что эффект последовательного сопротивления часто отсутствует. значительный, это может значительно снизить время моделирования, и это часто увеличивает ошибки округления. rstray по умолчанию для Совместимость со специями, и потому что это обычно важно для BJT модель.Norstray — это эквивалент установки модели параметры rd, rs и rsh равны нулю.

Ввод значения параметра 0 — это не то же самое, что не указывать Это. Такое поведение несовместимо со SPICE. В SPICE значение 0 часто интерпретируется как не указанное, в результате чего вычислить его другим способом. Если вы хотите, чтобы он был рассчитан, не указывайте это.

Еще одно тонкое отличие от SPICE заключается в том, что Gnucap может опускать некоторые ненужные части модели, которые могут повлиять на некоторые заявленные ценности.Это не должно влиять на напряжение или ток. Например, если затвор и слив связаны, Cgs в модели не будет, поэтому напечатанное значение для Cgdovl и Cgd будет 0, что будет не согласен со SPICE. Это не имеет значения, потому что закороченный конденсатор можно хранить бесплатно.

Реализованы уровни 1, 2, 3, 4, 5, 6, 7.

Основные параметры, совместимые со Spice

- L = x

- Длина вытяжного канала. (По умолчанию = параметр DEFL из options.DEFL по умолчанию = 100)

- W = x

- Ширина вытяжного канала. (По умолчанию = параметр DEFW из опций. DEFW по умолчанию = 100)