Логическая схема и принцип работы RS триггера в таблице истинности

Базовый строительный блок, который делает возможной компьютерную память, а также используется во многих последовательных логических устройствах является триггерной, или бистабильной, схемой. Только два взаимосвязанных логических входа составляют основную форму этой схемы, выход которой имеет два стабильных состояния. Когда схема запускается в какое-либо из них с помощью подходящего входного импульса, она будет «запоминать» это состояние до тех пор, пока оно не будет изменено дополнительным входным импульсом, или пока не отключится питание.

Логическая микросхема

Классификация последовательных схем

Последовательные схемы могут быть использованы для простых триггеров или для создания более сложных систем: устройств памяти, счетчиков, регистров сдвига. Они подразделяются на три основные категории:

- Асинхронные, меняющие статус при включении;

- Синхронные, согласованные с тактовым сигналом;

- Комбинированные, реагирующие на запуск импульсов.

Важно! Если схема зависит от внешнего входа, то она является асинхронной. Если состояния меняются в зависимости от тактового сигнала, то она синхронная. Для сохранения состояния присутствует обратная связь, когда частично сигнал с выхода идет опять на вход.

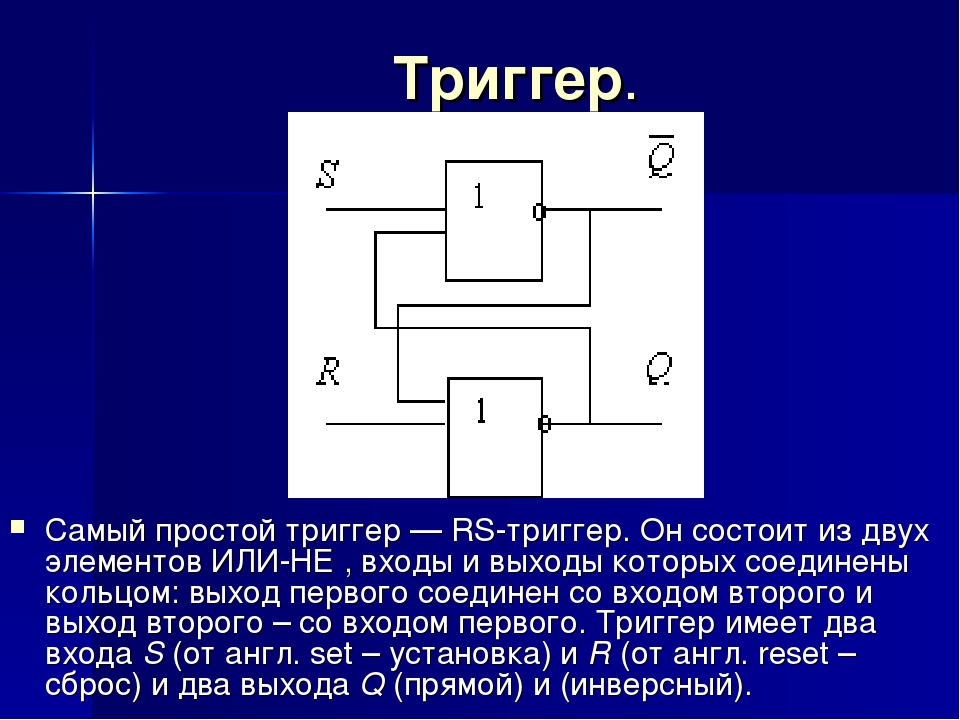

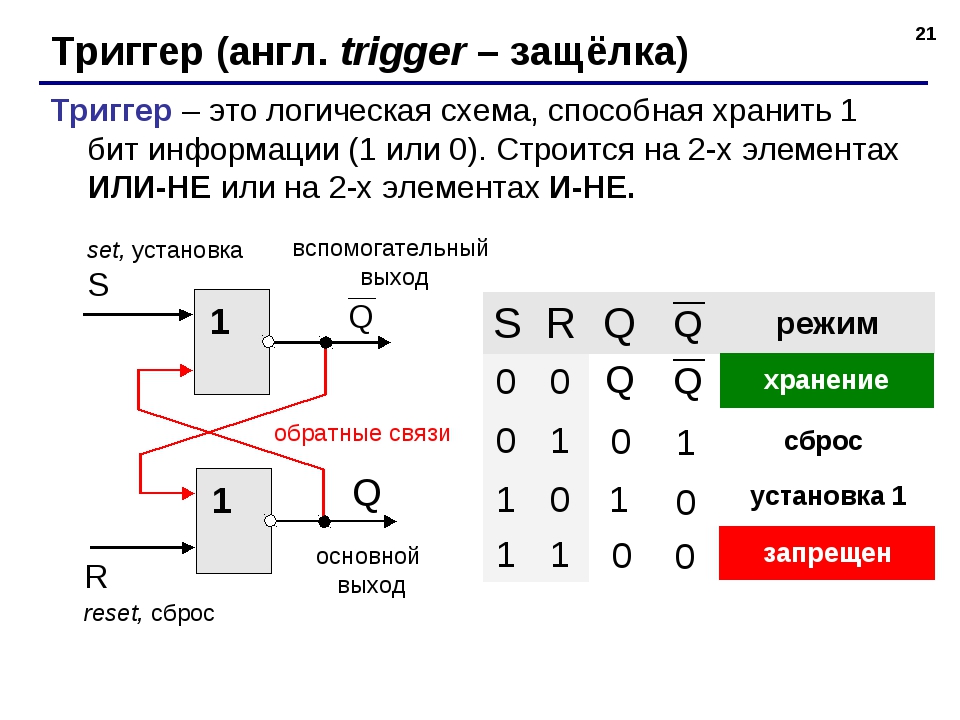

Что такое RS триггер

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

RS триггер

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ).

Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние.

Таблица истинности

Работу триггера РС можно представить в таблице истинности:

- Q устанавливается на логическое значение 1, если применяется 0 на входе S;

- Изменение S-входа на единицу на выходную логику не влияет. 0-импульс был запомнен Q;

- Q сбрасывается на 0 с помощью логического 0, подаваемого на вход R;

- Когда R возвращается к 1, на Q запоминается 0.

Таблица истинности

Для условий 2-й и 3-ей строки таблицы Q̃ является величиной, обратной Q. Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

В последней строке на обоих входах присутствует логическая единица, выходы Q̃ и Q будут находиться в противоположных состояниях, но не ясно, какими конкретно значениями будут обладать. Они будут соответствовать запоминаемым с последнего входного импульса.

Помимо применения логики И-НЕ, можно построить простые триггеры, используя два перекрестно соединенных вентиля И-ИЛИ. Схема работает аналогично. Только запрещенное состояние будет при наличии обоих входных сигналов, равных единице.

Временные диаграммы

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

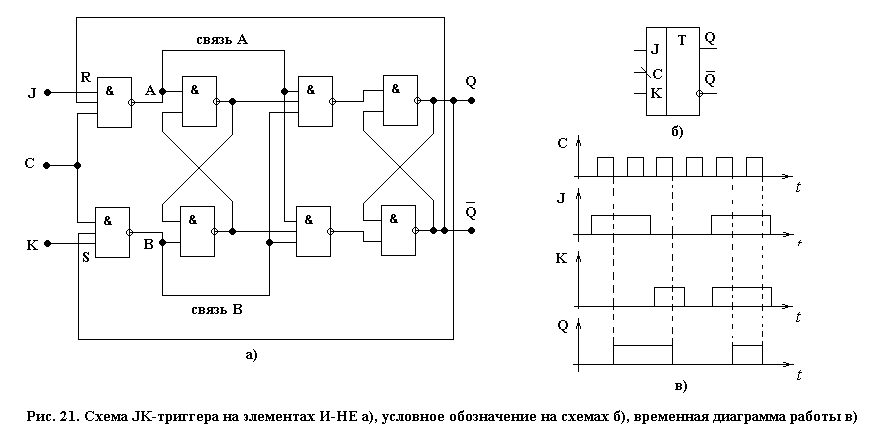

JK триггер

Другие широко распространенные виды логических схем – JK, D и Т, которые являются разработками RS триггера на логических элементах.

Недостатки схемы И-НЕ РС триггера:

- Необходимость избегать условия, когда оба входных сигнала равны 0;

- При изменениях состояния R и S, имеющих единичный входной сигнал, правильное блокирующее действие не всегда происходит.

Для преодоления этих недостатков была разработана схема JK триггера. Его входы являются теми же R и S, но им присвоены буквы J и K по имени изобретателя схемы, чтобы отличить от других триггеров. JK схема отличается от RS триггера тем, что она не имеет неопределенных или запрещенных входных статусов.

JK триггер

В JK добавлена входная схема синхронизации, предотвращающая неопределенное условие вывода, которое может случиться, если R и S равны единице. Поэтому в наличии четыре возможных комбинации ввода: 1, 0, «без изменений» и «переключение». Вход J соответствует S, а K – R. Кроме того, для каждого вентиля имеется третий вход. На выходе остаются Q̃ и Q.

Поэтому в наличии четыре возможных комбинации ввода: 1, 0, «без изменений» и «переключение». Вход J соответствует S, а K – R. Кроме того, для каждого вентиля имеется третий вход. На выходе остаются Q̃ и Q.

Перекрестная связь RS триггера позволяет использовать ранее неопределенные условия работы триггера, когда оба входных сигнала равны 1, для создания «переключателя», так как два входа могут быть блокированы.

Схема JK – это триггер SR с обратной связью, который позволяет только одному из его терминалов (SET или RESET) быть активным в любой момент времени, тем самым устраняя недопустимое условие:

- Если активен терминал SET, вход J блокируется статусом 0 (Q̃) через нижний логический элемент И-НЕ;

- Если в действии терминал RESET, вход К заблокирован статусом 0 через верхний вентиль И-НЕ.

Так как Q̃ и Q всегда разные, они могут использоваться для манипулирования входом. Для JK триггера таблица истинности принимает следующий вид.

Для JK триггера таблица истинности принимает следующий вид.

Таблица истинности JK триггера

Когда оба входа J и K имеют единицу на входе при высоком тактовом импульсе, схема может переключаться из состояния SET в RESET и наоборот.

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер.

При этом оба входа воспринимают сигналы R и S.

При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Видео

Оцените статью:|

Триггеры Триггеры имеют два устойчивых состояния.  Эти состояния

определяются по логическим уровням на выходах триггера. Триггер

снабжается двумя выходами: прямым Q и инверсным Q. Состояние триггера

определяет логический уровень на выходе Q. Говорят, что триггер находится в

состоянии логической единицы, если на выходе Q уровень напряжения,

соответствующий логической единице. Эти состояния

определяются по логическим уровням на выходах триггера. Триггер

снабжается двумя выходами: прямым Q и инверсным Q. Состояние триггера

определяет логический уровень на выходе Q. Говорят, что триггер находится в

состоянии логической единицы, если на выходе Q уровень напряжения,

соответствующий логической единице.Триггеры могут иметь входы различного типа: R (от англ. RESET) – раздельный вход установки в состояние 0; S (от англ. SET) – раздельный вход установки в состояние 1; К – вход установки универсального триггера в состояние 0; J – вход установки универсального триггера в состояние 1; V — вход разрешения; С — синхронизирующий вход; D — информационный вход; Т — счетный вход и некоторые другие.  Обычно название триггера дают по имеющимся у него входам: RS-риггер, JK-триггер, D-триггер и др. По способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах состояние на выходе изменяется сразу же после изменения сигнала на информационных входах. В синхронных триггерах для передачи сигнала с информационных входов на выходы требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигнала с информационных входов на выходы осуществляется по фронту или по спаду синхронизирующего импульса. Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера.  Цифровые автоматы, к

которым относятся триггеры, иногда называют последовательными схемами. Цифровые автоматы, к

которым относятся триггеры, иногда называют последовательными схемами. Триггеры строились по самым разнообразным электрическим схемам. В последнее время триггеры обычно конструируют, используя логические элементы. Рассмотрим два варианта RS-триггера: RS-триггер с прямыми входами и RS-триггер с инверсными входами. Установка триггера в нужное состояние осуществляется подачей уровня логической «1» на соответствующий вход для триггера с прямыми входами и подачей сигналов логического «0» для триггера с инверсными входами. Наибольшее распространение получили RS-триггеры, построенные на логических элементах 2И-НЕ или 2ИЛИ-НЕ. На рисунке 1.36,а приведена функциональная схема RS-триггера с инверсными входами на двух логических элементах 2И-НЕ, а на рисунке 1.36,б – его условное обозначение на принципиальных схемах.  RS- триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ. Триггер получается путем соединения выхода первого логического элемента с одним из входов второго и соединения выхода второго логического элемента с одним из входов первого. Как видно из получившейся схемы (рис. 1.37,а), по отношению к логическим элементам триггер симметричен. По этой причине не имеет принципиального значения, выход какого из элементов считать прямым выходом триггера. Допустим, что прямым выходом триггера является верхний вывод. Определим, какой из входов триггера является входом R, а какой – входом S. Вспомним, что активным логическим уровнем для элементов ИЛИ-НЕ является уровень логической единицы, т.е. если на входе элемента 2ИЛИ-НЕ действует логическая «1», то на выходе будет «0». Зная, что вход R – это вход установки триггера в нулевое состояние, приходим к выводу, что входом R в данном случае будет верхний вход RS-триггера.  Рассмотрим временную диаграмму работы RS-триггера с прямыми входами. Для RS-триггера нужно показать 4 графика (рис. 1.38). Пусть на входах R и S установлены пассивные для элементов ИЛИ-НЕ уровни логического нуля (пассивные логические уровни не могут изменить состояние триггера) и пусть триггер находится в единичном состоянии, т.е. на выходе Q уровень логической единицы. Подадим на вход R в момент времени t  Для анализа работы RS-триггера, как и любого

цифрового устройства, воспользуемся понятием активного логического

уровня. Это существенно облегчает анализ работы схемы. Если на одном

входе логического элемента действует активный логический уровень, то

нет необходимости анализировать логические состояния на других входах

элемента. Т.к. в момент времени t1 на входе

R элемента DD1.1 действует активный логический

уровень, то на выходе этого элемента, как

следует из таблицы истинности, будет уровень логического нуля. На

входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого

элемента уровень логической единицы. Мы видим, что состояние триггера

изменилось с единичного на нулевое. В момент времени t Для анализа работы RS-триггера, как и любого

цифрового устройства, воспользуемся понятием активного логического

уровня. Это существенно облегчает анализ работы схемы. Если на одном

входе логического элемента действует активный логический уровень, то

нет необходимости анализировать логические состояния на других входах

элемента. Т.к. в момент времени t1 на входе

R элемента DD1.1 действует активный логический

уровень, то на выходе этого элемента, как

следует из таблицы истинности, будет уровень логического нуля. На

входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого

элемента уровень логической единицы. Мы видим, что состояние триггера

изменилось с единичного на нулевое. В момент времени t В момент времени t3 В момент времени t3 В

момент времени t7 установим на входах R и S одновременно уровень логического

нуля. Состояние триггера в этом случае будет неопределенным. Может

оказаться, что на выходе Q логическая единица, а на выходе Q логический нуль, или наоборот.

Поэтому в устройствах цифровой техники одновременную подачу активных

логических уровней на входы R и S

триггера запрещают. Такой запрет делают не потому, что триггер выйдет

из строя, а потому, что состояние триггера неоднозначно после

одновременного снятия уровней логической единицы на входах R и S. В

момент времени t В

момент времени t7 установим на входах R и S одновременно уровень логического

нуля. Состояние триггера в этом случае будет неопределенным. Может

оказаться, что на выходе Q логическая единица, а на выходе Q логический нуль, или наоборот.

Поэтому в устройствах цифровой техники одновременную подачу активных

логических уровней на входы R и S

триггера запрещают. Такой запрет делают не потому, что триггер выйдет

из строя, а потому, что состояние триггера неоднозначно после

одновременного снятия уровней логической единицы на входах R и S. В

момент времени tРассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.  Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. На рисунках 1.39,а,в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 1.39,б. Рассмотрим функциональную схему синхронного RS-триггера, приведенную на рисунке 1.39а. При С=0 на входах R, S асинхронного триггера на элементах DD1.1 и DD1.2 действуют сигналы логического нуля (логический нуль является пассивным логическим уровнем для логических элементов 2ИЛИ-НЕ), поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется. При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше асинхронный RS-триггер с прямыми входами.  Рассмотренный только что синхронный RS-триггер относится к триггерам со статическим управлением.

Рассмотренный только что синхронный RS-триггер относится к триггерам со статическим управлением.

На рисунках 1.40,а и 1.41,а приведены функциональные схемы синхронных RS-триггеров с динамическим управлением, а их условные обозначения на принципиальных схемах соответственно на рисунках 1.40,б и 1.41,б. Если в обозначении синхронного RS-триггера с динамическим управлением стрелочка на входе С направлена к триггеру, то передача сигналов с информационных входов на выходы происходит по фронту импульса, а если стрелочка направлена от обозначения триггера, то передача сигнала осуществляется по спаду импульса. Рассмотрим синхронный RS-триггер с динамическим управлением, схема которого приведена на рисунке 1.40,а. Проанализировав функциональную схему синхронного RS-триггера с динамическим управлением, убедимся в том, что состояние триггера не меняется как при изменении сигналов на входах S и R при С=0, так и при С=1, если триггер переключился по фронту синхронизирующего импульса.  При C=0 на выходах элементов DD2.1, DD2.2 будут сигналы

логической единицы, и состояние на выходе триггера изменяться не будет

при любых изменениях сигналов на входах R и S. При C=0 на выходах элементов DD2.1, DD2.2 будут сигналы

логической единицы, и состояние на выходе триггера изменяться не будет

при любых изменениях сигналов на входах R и S. Установим на инверсном входе S уровень логического нуля, на инверсном входе R уровень логической единицы, и сигнал на входе С изменим с логического нуля на логическую единицу. На выходе элемента DD2.1 появится сигнал логического нуля и триггер перейдет в единичное состояние, или состояние триггера не изменится, если он находился в единичном состоянии. Оставляя на входе С сигнал логической единицы, перевести триггер в нулевое состояние не удается. Для перевода триггера в противоположное состояние обязательно необходимо подать синхронизирующий импульс. В синхронных RS-триггерах со статическим управлением остается неоднозначность состояния на выходе триггера, если с входов R, S одновременно убирать активные уровни сигналов.  Для устранения неоднозначности в схему синхронного RS-триггера добавляют логический

элемент «НЕ». Получившийся триггер является D-триггером со статическим

управлением. Функциональная схема этого триггера приведена на рисунке

1.42,а, а его условное обозначение на принципиальных схемах – на

рисунке 1.42,б. Для устранения неоднозначности в схему синхронного RS-триггера добавляют логический

элемент «НЕ». Получившийся триггер является D-триггером со статическим

управлением. Функциональная схема этого триггера приведена на рисунке

1.42,а, а его условное обозначение на принципиальных схемах – на

рисунке 1.42,б. При С=0 состояние триггера изменяться не будет какой бы ни был сигнал на входе D, т.к. на выходах элементов DD2.1, DD2.2 будут сигналы логических нулей. При С=1 и D=1 на выходе элемента DD2.1 появится сигнал логического нуля, а на прямом выходе D-триггера – сигнал логической единицы. При С=1 и D=0 сигнал логического нуля появится на выходе элемента DD2.2, на инверсном выходе D-триггера установится логическая единица, а на прямом выходе –логический нуль. Таким образом, D-триггер воспринимает информацию с входа D и передает ее на выход Q при C=1, и затем хранит ее сколько угодно долго (пока подключен источник питания) при С=0.  Т.е. мы имеем ячейку памяти для хранения 1

бита информации. Т.е. мы имеем ячейку памяти для хранения 1

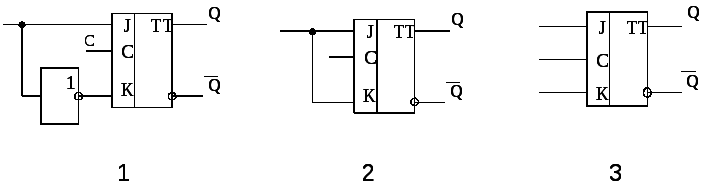

бита информации. На рисунке 1.43,а приведен еще один вариант схемы D-триггера со статическим управлением. Условное обозначение обоих этих триггеров одинаковое. Временная диаграмма работы D-триггера со статическим управлением приведена на рисунке 1.44. Из диаграммы следует, что передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса. Счетный триггер из данного триггера путем соединения инверсного выхода с входом D получить нельзя. Из D-триггера можно легко получить DV-триггер. Вместо логических элементов 2И-НЕ используют логические элементы 3И-НЕ и делают дополнительно вход разрешения V. Функциональная схема DV-триггера и его условное обозначение на принципиальных схемах показаны соответственно на рисунке 1.45,а-б. Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.  Функциональная схема D-триггера с передачей

информации с входа на выход триггера по фронту синхронизирующего

импульса приведена на рисунке 1.46,а, а его условное обозначение на

принципиальных схемах – на рисунке 1.46,б. Функциональная схема D-триггера с передачей

информации с входа на выход триггера по фронту синхронизирующего

импульса приведена на рисунке 1.46,а, а его условное обозначение на

принципиальных схемах – на рисунке 1.46,б. При С=0 на выходах элементов DD1.3, DD1.4 будут сигналы логических единиц и состояние на выходе триггера не изменится при любых изменениях сигнала на входе D. Установим на входе D сигнал логической единицы и изменим на входе С сигнал с логического нуля на единицу. Перед подачей на вход С сигнала логической единицы на выходе элемента DD1.2 логический нуль, а на верхнем входе элемента DD1.3 логическая единица. При появлении на входе С логической единицы на выходе элемента DD1.3 установится логический нуль, а на прямом выходе триггера – логическая единица. Сигнал логического нуля подается с выхода элемента DD1.3 на нижний вход элемент DD1.1 и на верхний вход элемента DD1.4. Оставляя на входе С логическую единицу, изменим сигнал на входе D с логической единицы на нуль. На выходе элемента DD1.2 установится логическая единица, а сигналы на выходах элементов DD1.1, DD1.3 не изменятся, следовательно, не изменится состояние на выходе триггера. При D=0 изменим сигнал на входе С с логической единицы на нуль. На выходах элементов DD1.3, DD1.4 будут логические единицы, а на прямом выходе триггера останется сигнал логической единицы. Затем изменим сигнал на входе С с логического нуля на логическую единицу. На выходе DD1.4 установится логический нуль, на инверсном выходе триггера логическая единица, а прямом выходе – логический нуль. Из анализа работы данного триггера следует, что в нем передача информации с входа D на выход Q осуществляется по фронту синхронизирующего импульса, подаваемого на вход С. Триггеры являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением легко превратить в счетный триггер. С этой целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий вход. Схема такого соединения приведена на рисунке 1.46,в. Находят применение двухтактные RS-триггеры (рис. 1.47,а). На рисунке 1.47,б приведена схема счетного триггера, построенного на основе двухтактного RS-триггера. Двухтактный RS-триггер состоит из двух триггеров: главного и вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера. Используя двухтактные RS-триггеры, можно построить JK-триггер. В JK-триггере устранена неопределенность, возникающая в RS-триггере при одновременном снятии активных логических сигналов с входов R и S. Функциональная схема JK-триггера, построенного с использованием двухтактных (двухступенчатых) RS-триггеров, приведена на рисунке 1.48,а, а его условное обозначение на принципиальных схемах – на рисунке 1.48,б. В условных обозначениях триггеров, построенных с использованием двухтактного синхронного RS-триггера, ставят две буквы Т. Если входы J и K данного триггера соединить вместе и подать на них сигнал логической единицы, а импульсы подавать на вход С, то получим счетный триггер. Широкое распространение получили JK-триггеры, построенные с использованием синхронных RS-триггеров с динамическим управлением. На рисунке 1.49,а приведена функциональная схема JK-триггера, переключающегося по спаду синхронизирующего импульса, а условное обозначение этого триггера на принципиальных схемах приведено на рисунке 1.49,б. Элементы DD1.1, DD1.2 образуют асинхронный RS-триггер. Функциональная схема JK-триггера, переключающегося по фронту синхронизирующего импульса, показана на рисунке 1.50,а, а условное обозначение приведено на рисунке 1.50,б. При С=0 на выходах элементов DD2.1 и DD2.2 логические единицы и состояние RS–триггера DD3 не изменяется. Если на инверсных входах J и K логические единицы, то переключение сигнала на входе С с логического нуля на логическую единицу не изменит состояние на выходе JK–триггера. На рисунке 1.50,в приведена схема использования JK-триггера в качестве счетного. На входы J и K подаются логические нули, а импульсы подаются на вход С. Вход С в данном случае является счетным входом Т. Частота импульсов на выходе данного счетчика в два раза меньше частоты импульсов на входе. Скважность импульсов на выходе счетчика равна двум независимо от скважности импульсов на входе счетчика. Напомним, что триггеры относятся к цифровым автоматам. Цифровые автоматы состоят из комбинационных схем. Триггеры входят в состав счетчиков электрических импульсов, регистров, запоминающих устройств. Один из универсальных сдвиговых регистров рассмотрен в главе 2. Перейдем к рассмотрению счетчиков и запоминающих устройств. |

НОУ ИНТУИТ | Лекция | Триггеры

Аннотация: В лекции рассказывается о триггерах различных типов, об алгоритмах их работы, параметрах, типовых схемах включения, а также о реализации на их основе некоторых часто встречающихся функций.

Триггеры и регистры являются простейшими представителями цифровых микросхем, имеющих внутреннюю память. Если выходные сигналы логических элементов и комбинационных микросхем однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Именно поэтому их применение позволяет строить гораздо более сложные и интеллектуальные цифровые устройства, чем в случае простейших микросхем без памяти. Микросхемы с внутренней памятью называются еще последовательными или последовательностными, в отличие от комбинационных микросхем.

Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания. Иначе говоря, их память относится к типу оперативной (в отличие от постоянной памяти и перепрограммируемой постоянной памяти, которым отключение питания не мешает сохранять информацию). После выключения питания и его последующего включения триггеры и регистры переходят в случайное состояние, то есть их выходные сигналы могут устанавливаться как в уровень логической единицы, так и в уровень логического нуля. Это необходимо учитывать при проектировании схем.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Именно поэтому триггеры и регистры иногда называют также сверхоперативной памятью. Однако недостаток триггеров и регистров в том, что объем их внутренней памяти очень мал, они могут хранить только отдельные сигналы, биты (триггеры) или отдельные коды, байты, слова (регистры).

Триггер можно рассматривать как одноразрядную, а регистр — как многоразрядную ячейку памяти, которая состоит из нескольких триггеров, соединенных параллельно (обычный, параллельный регистр) или последовательно (сдвиговый регистр или, что то же самое, регистр сдвига).

Триггеры

Принцип работы и разновидности триггеров

В основе любого триггера (англ. — «тrigger» или «flip-flop») лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

Рис. 7.1. Схема триггерной ячейки

Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

| Входы | Выходы | ||

|---|---|---|---|

| -R | -S | Q | -Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Без изменения | |

| 0 | 0 | Не определено | |

В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

- RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый (а).

- JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко (б).

- D-триггер (обозначается ТМ) — наиболее распространенный тип триггера (в).

Примером RS-триггера является микросхема ТР2, в одном корпусе которой находятся четыре RS-триггера. Два триггера имеют по одному входу –R и –S, а два других триггера — по одному входу –R и по два входа –S1 и –S2, объединенных по функции И. Все триггеры имеют только по одному прямому выходу. RS-триггер практически ничем не отличается по своим функциям от триггерной ячейки, рассмотренной ранее (см. рис. 7.1). Отрицательный импульс на входе –R перебрасывает выход в нуль, а отрицательный импульс на входе –S (или на любом из входов –S1 и –S2) перебрасывает выход в единицу. Одновременные сигналы на входах –R и –S переводят выход в единицу, а после окончания импульсов триггер попадает случайным образом в одно из своих устойчивых состояний. Таблица истинности триггера ТР2 с двумя входами установки –S1 и –S2 представлена в табл. 7.2.

Рис. 7.2. Триггеры трех основных типов

| Входы | Выходы | ||

|---|---|---|---|

| -R | -S | Q | -Q |

| 1 | 1 | 1 | Без изменения |

| X | 0 | 1 | 1 |

| 0 | X | 1 | 1 |

| 1 | 1 | 0 | 0 |

| X | 0 | 0 | Не определен |

| 0 | X | 0 | Не определен |

JK-триггер значительно сложнее по своей структуре, чем RS-триггер. Он относится к так называемым тактируемым триггерам, то есть он срабатывает по фронту тактового сигнала. Примером может служить показанная на рис. 7.2 микросхема ТВ9, имеющая в одном корпусе два JK-триггера со входами сброса и установки -R и -S. Входы -R и -S работают точно так же, как и в RS-триггере, то есть отрицательный импульс на входе -R устанавливает прямой выход в нуль, а инверсный — в единицу, а отрицательный импульс на входе -S устанавливает прямой выход в единицу, а инверсный — в нуль.

Однако состояние триггера может быть изменено не только этими сигналами, но и сигналами на двух информационных входах J и K и синхросигналом С. Переключение триггера в этом случае происходит по отрицательному фронту сигнала С (по переходу из единицы в нуль) в зависимости от состояний сигналов J и K. При единице на входе J и нуле на входе К по фронту сигнала С прямой выход устанавливается в единицу (обратный — в нуль). При нуле на входе J и единице на входе К по фронту сигнала С прямой выход устанавливается в нуль (обратный — в единицу). При единичных уровнях на обоих входах J и K по фронту сигнала С триггер меняет состояние своих выходов на противоположные (это называется счетным режимом).

Рис. 7.3. Временная диаграмма работы JK-триггера ТВ9

Таблица истинности триггера ТВ9 представлена в табл. 7.3, а временная диаграмма работы — на рис. 7.3.

Персональный сайт — Триггеры

Триггер — это запоминающее устройство, хранящее одно из двух состояний — либо 0 либо 1.

Содержание

Является синхронным триггером

Таким образом триггер сохраняет значение поданное на вход D.

Рис. 14. Условное обозначение D-триггера, его реализация и временные диаграммы его работы.

Рис. 15. Временные диаграммы.

При C=0 и R=S=1 возникает запрещенное состояние.

Предназначен для хранения информации на входе D при C=1

Рис. 16. Условное обозначение T-триггера.

Триггер при подаче сигнала синхронизации меняет значение на выходе на противоположное. Может иметь вход стробирования Е (при Е=0 триггер не изменяет значение на выходе ни при каких условиях).

Рис. 17. Схема T-триггера.

Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим.

Может быть реализован и на синхронном RS-триггере (рис. 5.3).

Рис. 18. Реализация T-триггера на базе RS-триггера.

Короткие импульсы синхронизации (менее времени срабатывания триггера) не совсем удобны для управления триггерами. Как вариант модернизации существуют двухступенчатые триггеры. Они реагируют на смену значения на входе синхронизации (фронт:0-1, либо спад:1-0).

В основе — RS триггер.

Рис. 19. Общий вид двухступенчатых триггеров.

Перезапись из первой во вторую ступень происходит при смене значения входа синхронизации.

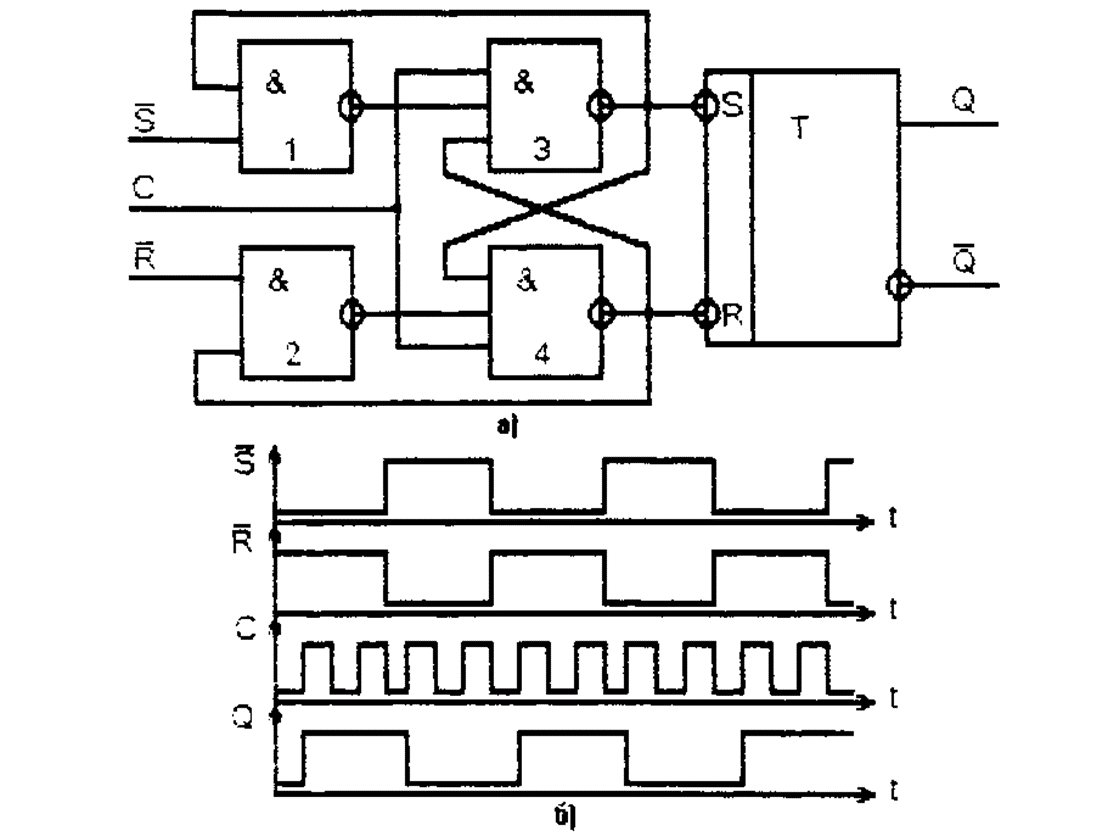

Двухступенчатый синхронный RS-триггер

Рис. 20. Схема двухступенчатого синхронного RS-триггера.

Запись происходит по спаду (изменение с 1 до 0). Основа — два обычных RS-триггера. Запись в первый триггер происходит при С=1 (второй триггер в это время в режиме хранения). При смене значения С на С=0 происходит запись значений из первого триггера во второй. Таким образом запись происходит по спаду сигнала синхронизации С (это обозначается наклонной чертой на входе синхронизации в обозначении триггера на схеме — см. рис 6.3).

Рис. 21. Условное обозначение двухступенчатого синхронного RS-триггера.

Двухступенчатый D-триггер

Рис. 22. Схема и условное обозначение двухступенчатого D-триггера.

Логика работы та же что и у RS-триггера. С=1 — запись в первый триггер, С=0 — запись из первого во второй (запись по спаду).

Двухступенчатый JK-триггер

Рис. 23. Схема двухступенчатого JK-триггера.

Поведение аналогично предыдущим триггерам кроме состояния J=1 K=1. Рассмотрим это состояние. При J=1K=1 и C=1 возникает автоколебательный процесс: 0, 1, 0, 1 и т.д. JK-триггер должен переключаться в состояние, противоположное тому, в котором находится 2-й триггер, т.е. используются только внутренние обратные связи (ОС).

Для устранения этого недостатка можно модифицировать схему (рис. 24)

Рис. 24. Схема двухступенчатого JK-триггера (без автоколебательного процесса).

Особенность схемы — наличие глубокой обратной связи (а именно, связи выходов второй ступени со входами первой ступени). В результате в триггер первой ступени записываются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно).

Двухступенчатые триггеры изменяют свои значения по спаду/фронту синхроимпульса, поэтому длительность импульсов не важна.

Приведенные выше (рис. 23 и 24) схемы являются базовыми, теперь следует рассмотреть конкретные реализации.

Рис. 25. Реализация двухступенчатого JK-триггера на базе элементов «И-НЕ».

На входы D1 и D2 идет обратная связь с выходов D7, D8. Запись происходит при условии, что на выходах D1 и D2 одновременно присутствуют «1» (запись во вторую ступень). Запись в первую ступень происходит при противоположных значениях на выходах D7, D8. Запись в первую ступень происходит либо при C=1, либо при J=K=0. Перезапись — при C=0 (на выходах D1 и D2 — единицы).

Еще эту схему можно получить на базе RS-триггеров (вывод схемы — на рис. 26)

Рис. 26. Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).

Рис. 27. Пример универсального триггера.

При необходимости в схему можно ввести асинхронные входы установки в 0 и 1 — они устанавливают схему независимо от схемы управления. Триггер сч такими входами называется универсальным (т.е. он имеет и синхронные. и асинхронные входы установки). Асинхронные входы нужны для инициализации. Пример — рис 27, вход Reset переустановка всех компонентов схемы в начальное состояние. В режиме хранения требуется реагирование на синхронные входы (на их значения). При режиме записи — приоритет у асинхронных входов.

Универсальный JK-триггер

Рис. 28. Обозначение универсального JK-триггера.

Имеет как синхронные, так и асинхронные входы установки. Конъюнкции D1 и D2 могут быть и 3х-входовыми, и 6-тивходовыми, а могут иметь и большую размерность, следовательно, вместо одного сигнала J приходят несколько сигналов, объединенных конъюнкциями. Другими словами, на входе появляется «1», если на всех J — «1». Для входа K ситуация аналогичная.

Классическая схема ступенчатого D-триггера представлена на рисунке 29.

Рис. 29. Разработка ступенчатого D-триггера.

Состоит из трех асинхронных RS-триггеров (состоят из D1-D2, D3-D4, D5-D6 соответственно). Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

T3 — с инверсными входами (рем хранение — оба значения равны «1»). Если C=0, то T2=T3=1, то есть при C=0T3=1, а при C=1 T3 определяется тем, что подается на вход D.

При C=0,D=0 в T1 записывается некоторое значение, а T2 находится в запрещенном состоянии (две «1»).

Если при C=1 T2=1 и T3=0, то произойдет переход в режим записи и произойдет запись «0» во вторую ступень.

Рассмотрим случай, когда C=0,D=1. Пусть D4=0, вход D4=0, тогда D1=1, можно наблюдать противоположную картину: T2 находится в режиме записи значения, а T1 — в запрещенном состоянии.

Рис. 8.2. Условное обозначение ступенчатого D-триггера.

При переключении C из «0» в «1» на D3 происходит то же изменение, что и на D2 — переход из 1 в 0. Тогда T3 находится в режиме записи логической единицы:

(0)Q→1 (1)¯Q→0При C=1 значение на входе D поменяется: 1→0, выход D4 установится в значение логической «1», поэтому D1 станет равным 1 (его значение на выходе не меняется, на D2 — то же самое (только там — логический 0), поэтому значение на выходе D3 не меняется за счет D1 и D2).

При C=1 значение на входе D изменяется в порядке 1→0→1, значение D3 меняться не будет. Следовательно, при C=0 на выходе значение не будет меняться, при C=1 значение на выходе тоже не меняется. Таким образом, запись производится при переключении с 0 на 1 (по фронту).

- Первый триггер — для фиксации того, что хотим записать «0»;

- Второй триггер — для фиксации того, что хотим записать «1».

В итоге, при C:0→1 происходит запись, то есть переключение в другое состояние (или в запрещенное состояние).

Рис. 30. Условное обозначение ступенчатого D-триггера.

Рис. 31. Преобразование ступенчатого D-триггера в универсальный.

Рис. 32. Условное графическое обозначение универсального D-триггера.

Триггеры Асинхронный RS-триггер T- триггеры Синхронный RS…

Сразу хочу сказать, что здесь никакой воды про триггер, и только нужная информация. Для того чтобы лучше понимать что такое триггер, асинхронный rs-триггер, t-триггеры, синхронный rs триггер, d-триггер, jk-триггер , настоятельно рекомендую прочитать все из категории Электроника, Микроэлектроника , Элементная база

триггер ы

Основные понятия

Триггер — электронное устройство, которое может сохранять одно из двух возможных состояний.

Входы триггера подразделяются на:

установочные — для установки начального состояния триггера;

информационные — для ввода информации;

исполнительные — для задания момента срабатывания триггера.

Триггеры запускаются по фронту или по срезу

Обозначения воздействия исполнительного импульса

асинхронный rs-триггер

S — set – установка в «1» Обозначение

R – reset – сброс в «0»

RS – триггер асинхронный, т.е . Об этом говорит сайт https://intellect.icu . переход из одного состояния в другое не связано с тактовыми сигналами.

Таблица истинности RS-триггера

Временные диаграммы асинхронного RS-триггера

синхронный rs триггер

Обозначение

Предварительно на Q=«1», изменение на «0» возможно, когда наR и C «1», если надо на Q=1, то S=1 и C=1 и т.д.

Временные диаграммы

d-триггер

D-триггер – (триггер задержки данных delay ) — синхронный триггер, выходное состояние которого совпадает с сигналом на его информационном входе (D-входе), которое тот имел на предыдущем такте импульсов синхронизации

Условное обозначение и Таблица истинности срабатывания триггера по фронту

Временные диаграммы

D-триггер задерживает на 1 такт информацию, существующую на входе D.

На D – триггерах могут быть построены регистры , чтобы заполнить 8-ми разрядное слово надо 8 D-триггеров.

Информация в D-триггерах хранится до тех пор, пока не придет разрешение на смену информации и тогда запишется другое число

T- триггеры

Счетный триггер (Т-триггер) изменяет свое состояние всякий раз при наличии активного уровня сигнала на его единственном информационном входе Т.

Обозначение

Т-триггер – делитель частоты на 2.

Временные диаграммы

Таблица истинности

jk-триггер (универсальный)

Обозначение Таблица истинности

Временные диаграммы

Если соединить J и k, то получаем Т-триггер. Т-триггер, при С=1

D-триггер на JK-триггере

А как ты думаешь, при улучшении триггер, будет лучше нам? Надеюсь, что теперь ты понял что такое триггер, асинхронный rs-триггер, t-триггеры, синхронный rs триггер, d-триггер, jk-триггер и для чего все это нужно, а если не понял, или есть замечания, то нестесняся пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Электроника, Микроэлектроника , Элементная база

Урок 8.4 Триггеры, регистры, счетчики

На предыдущем уроке мы рассмотрели логические элементы, состояние сигнала на выходе которых однозначно определяется состояниями сигналов на входах.

Логические элементы служат основой для создания более сложных цифровых устройств, одним из которых является триггер. Триггер – это целый класс электронных устройств, которые могут длительно находиться в одном из двух устойчивых состояний после прекращения сигнала, меняющего состояние. Состояние выхода триггера определяется не только сигналами на его входах, но и предыдущим состоянием устройства. Таким образом, триггер является простейшей однобитной ячейкой памяти.

RS-триггер

Самый простой триггер можно получить из двух логических элементов 2ИЛИ-НЕ:

Cхемотехническое обозначение:

Такая схема представляет собой асинхронный RS-триггер.

Он имеет два входа: S (set) – установка, R (reset) – сброс, и два выхода: Q (прямой) и Q с чертой сверху (инверсный, НЕ_Q).

При подаче сигнала логического нуля на оба входа триггера, его выходы будут установлены в произвольное состояние. Допустим, Q = 0, а НЕ_Q =1. Если на вход S подать «1», то состояние выхода Q скачкообразно изменится на «1», а НЕ_Q — на «0». И это состояние будет поддерживаться в независимости от того «0» или «1» подано на вход S, что и является проявлением свойства памяти.

Соответственно, при подаче уровня «1» на вход R выход Q станет «0», а НЕ_Q – «1».

Длительность устанавливающих импульсов может быть очень короткой, и ограничена физическим быстродействием логических модулей, из которых построен триггер.

Ситуация, когда на входах R и S действует высокий уровень, является недопустимой, поскольку при этом схема не может работать корректно. В этом есть недостаток RS-триггера.

RS-триггер также можно построить из двух элементов И-НЕ, такие элементы более распространены:

Установка и сброс триггера на элементах 2И-НЕ, в отличие от предыдущего, производится низким уровнем входного сигнала.

Если к последней схеме добавить еще два вентиля 2И-НЕ, то мы получим синхронный RS-триггер.

Изменение состояния такого триггера производится только при воздействии на вход С (Clock) синхронизирующего (тактового) импульса.

D-триггер

Немного изменив схему синхронного RS-триггера, можно получить D-триггер. (D-delay, задержка). У него только один информационный вход D.

Если на этот вход подать «1», а затем подать импульс на вход C, то на выходе Q будет «1», если на вход подать «0», затем импульс на C, то на выходе Q будет «0». Таким образом, D-триггер осуществляет задержку информации, поступающей на вход.

Если вход D соединить с выходом НЕ_Q, то триггер будет менять свое состояние при каждом изменении состояния входа С от «0» к «1» . При изменении от «1» к «0» состояние триггера меняться не будет. Таким образом, частота выходных импульсов будет вдвое меньше частоты входных импульсов. Такой триггер называется счетным или T-триггером. Делитель частоты используется очень широко в цифровой технике.

Существует разновидность синхронного RS-триггера, не имеющая запрещенной комбинации – JK-триггер. Он имеет три входа: J (вместо R), K (вместо S), и C. Если на оба информационных входа подана «1», то JK-триггер работает как счетный T-триггер с входом C.

Регистр хранения

На триггерах можно строить более сложные цифровые устройства, например такие, как регистры. Регистры предназначены для хранения многобитовой информации, то есть чисел, записанных в двоичном коде.

Рассмотри трех битовый регистр хранения на D-триггерах:

Каждый триггер может хранить один разряд (бит) числа. Вход R служит для установки выходов всех триггеров в нулевое (исходное) состояние перед записью числа, которое подается на входы D0,D1 и D2. При подаче импульса на вход C производится запись информации с этих входов. Информация может храниться сколь угодно долго, пока на вход С не подаются импульсы и подается питание.

Регистр сдвига

Другой разновидностью регистров является регистр сдвига. Он предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. На следующем рисунке приведена схема простейшего регистра сдвига информации вправо (по схеме):

В отличие от регистра хранения выход предыдущего триггера соединен с входом последующего. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд.

Сдвиговые регистры используются во многих схемотехнических решениях при построении цифровых устройств, прежде всего для преобразования последовательного кода в параллельный, а также для выполнения арифметических операций (умножения и деления на 2)с двоичными числами, организации линий задержки, формирования импульсов заданной длительности, генерирования псевдослучайных последовательностей (кодов) и т.п.

Счетчик

Еще один класс цифровых устройств, которые можно построить на триггерах – счетчики. Как следует из названия, они осуществляют счет входных импульсов в заданном коде и могут хранить результат.

Простейший счетчик с последовательным переносом можно получить с помощью счетных T-триггеров:

Подачей импульса на вход R счетчик приводится в исходное состояние, когда на выходах Q1-Q3 – уровень логического нуля.

На вход C подаются импульсы для счета. С приходом заднего фронта первого импульса первый (левый) по схеме триггер устанавливается в «1». Если читать код справа налево, то он соответствует единице. Для нашего трехразрядного счетчика это код 001. С приходом второго импульса в «1» переключается второй триггер, а первый переключается в «0». Таким образом, код на выходах счетчика будет 010, что соответствует десятичной цифре 2. Следующий импульс установит код 011, то есть 3. Трехразрядный счетчик может досчитать до кода 111, что соответствует десятичной цифре 7. При этом наступает так называемое переполнение счетчика, и с приходом следующего импульса счетчик обнулится.

Поскольку триггеры счетчика соединены последовательно, то и переключаться они будут также последовательно. Этот процесс отображен на графике, из которого видно, что время задержки переключения tз будет удваиваться и утраиваться. С увеличением числа разрядов задержка может оказаться неприемлемой, что является недостатком счетчиков с последовательным переносом.

Для повышения быстродействия применяются счетчики с параллельным переносом, что достигается одновременной подачей входных импульсов на входы всех триггеров счетчика. Это реализуется с помощью введения в схему логических элементов И:

Из схемы видно, что на вход второго триггера счетный импульс поступит только тогда, когда на выходе первого триггера будет «1», а на третий – когда «1» будет на выходах и первого, и второго триггеров. Очевидно, что с увеличением числа разрядов необходимо увеличивать как число логических элементов И, так и число их входов, что, в свою очередь, является недостатком такого типа счетчиков.

Регистры и счетчики, в свою очередь, могут применяться для построения более сложных цифровых устройств: сумматоров, ОЗУ и ПЗУ (оперативных и постоянных запоминающих устройств), АЛУ (арифметическо-логических устройств), входящих в состав процессоров, и так далее, к все более сложным цифровым устройствам.

В следующей серии статей мы начнем знакомство с микроконтроллерами — замечательным классом цифровых микросхем, которые являются настоящими компьютерами, умещающимися в одной микросхеме, и входящими входят в состав большинства электронных устройств, от кофемашины до космического корабля!

2.2 Синхронный rs-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс, то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера изображена на рис.10.

Рис. 10. Схема синхронного RS-триггера

Таблица 4 — Таблица переходов синхронного RS-триггера

R (S) | S | Q(t) | Q(t+1) | Пояснения |

0 | 0 | 0 | 0 | Режим сохранения информации R=S=0 |

0 | 0 | 1 | 1 | |

0 | 1 | 0 | 1 | Режим установки единицы S=1 |

0 | 1 | 1 | 1 | |

1 | 0 | 0 | 0 | Режим установки нуля R=1 |

1 | 0 | 1 | 0 | |

1 | 1 | 0 | * | R=S=1 запрещенная комбинация |

1 | 1 | 1 | * |

Под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние. При С=0 триггер отключен от управляющих S и R входов и находится в режиме хранения ранее полученной информации. При С=1 схема функционирует как обычный RS-триггер.

Характерной особенностью схемы является то, что в течение всего отрезка времени, когда синхросигнал равен 1, как сами потенциалы на управляющих S и R входах, так и любые их изменения тут же передаются на выход.

По аналогии с RS-триггером проверяем работоспособность синхронного RS-триггера. Для примера воспользуемся теми же параметрами входных информационных сигналов, какие были в примере работоспособности RS-триггера, а для сигнала синхронизации зададим следующие данные (рис.11).

Рис. 11. Параметры синхронизирующего сигнала.

2.3 Универсальный jk-триггер.

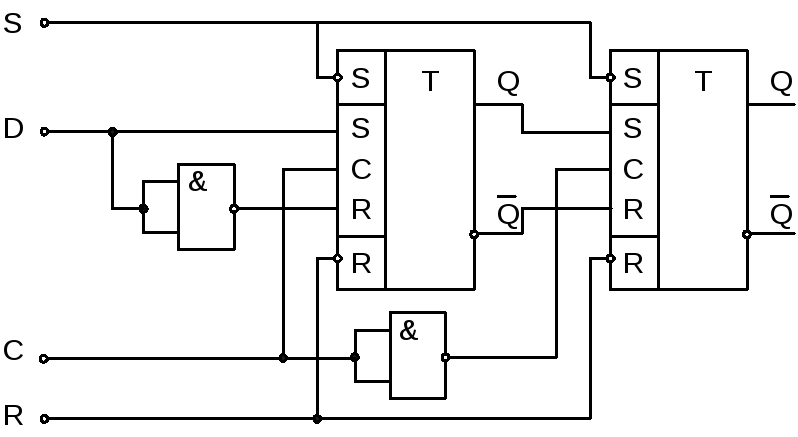

Универсальный JK-триггер, схема которого (рис.12) представляет собой двухступенчатый синхронный триггер. Как видно из рисунка, JK-триггер состоит из двух асинхронных RS-триггеров с инверсными входами и двух КЦУ, каждое из которых содержит две схемы И-НЕ с тремя входами каждая.

Закон функционирования JK-триггера задается (табл. 4). JK-триггер отличается от синхронного RS-триггера тем, что не имеет запрещенных комбинаций сигналов на входах J и К. Кроме того, при J=1 и K=1 триггер изменяет свое состояние на противоположное, т. е. работает как триггер со счетным входом (T-триггер).

Таблица 4 – Таблица переходов JK триггера

Сt | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

Jt | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

Kt | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

Qt | Qt | Qt | Qt | Qt | Qt | Qt | Qt | Qt |

Рис. 12 — Структура схема универсального JK-триггера

При С=0 входы J и К заблокированы и, следовательно, оказываются заблокированными входы S и R ведущего триггера 1. При С=1 в соответствии с информационными сигналами на входах J и К устанавливается состояние ведущего триггера. При этом на входы S и R ведомого триггера 2 поступают сигналы, при которых его предыдущее состояние сохраняется. При С=0, когда входы триггера 1 закрыты для входной информации, входы триггера 2 открываются и состояние ведущего триггера воспринимается ведомым триггером. В качестве запускающего импульса используем R, представляющий собой импульс небольшой длительности. Графическое обозначение JK-триггера (рис.13).

Рис. 13. Графическое обозначение JK-триггера.

Нарисуем принципиальную схему триггера (рис. 14).

Рис.14 Принципиальная схема JK-триггера.

Создаем отдельный элемент JK-триггер (рис. 15).

Рис.15. Элемент JK-триггер.

Осталось создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла. Пропишем в нём следующие строки (рис.16).

Рис.16

Дальнейший шаг – проверка работоспособности схемы, для этого производим симулирование. Для входных сигналов вводим исходные значения и получаем результат в виде графиков (рис.17).

Рис.17. Симулирование работы схемы

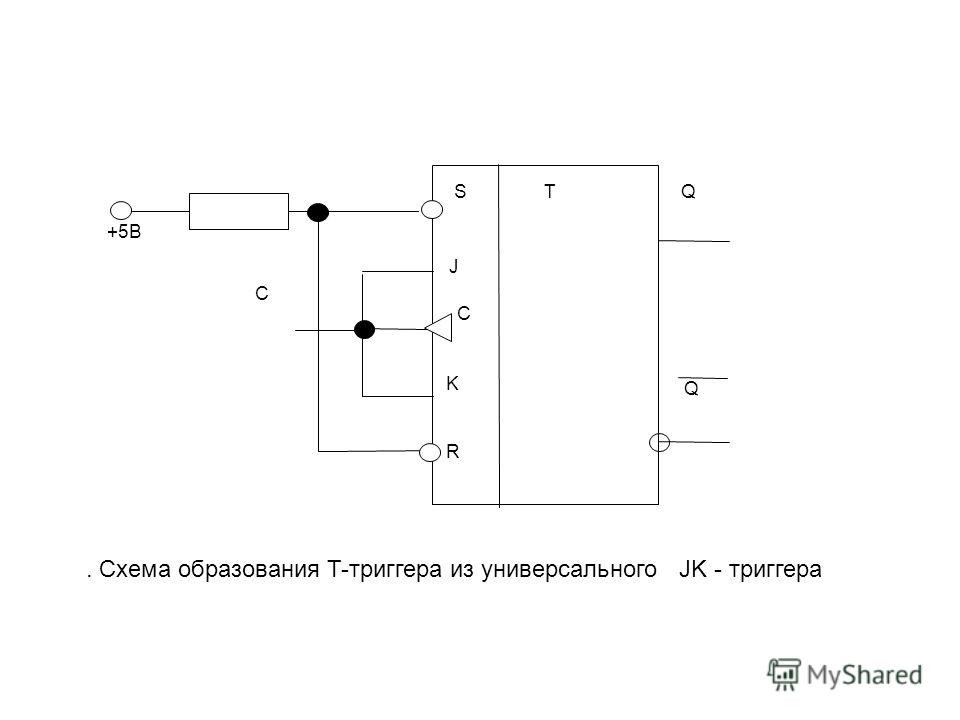

2.4 Т-триггер.

T-триггеры, или триггеры со счетным входом, могут быть получены из JK-триггера при соединении обоих информационных входов J и K. и подаче на них уровня 1. Функционирование T-триггера описывается (табл. 5) В качестве счетного входа T используется вход С. При подаче сигнала на вход T-триггер будет переключаться в состояние, противоположное предыдущему. JK-триггер в таком режиме выполняет функцию T-триггера.

Таблица 5 – Таблица переходов Т триггера

Сt | Jt | Kt | Qt | Qt+1 |

0 | 1 | 1 | Qt | Qt |

1 | 1 | 1 | Qt |

Рис. 18 — Построение Т-триггера на базе JK-триггера.

Следует заметить, что уровень 1 для входов J и К (входов элементов И-НЕ) является пассивным сигналом. Поэтому для получения T-триггера из JK-триггера можно не предусматривать входы J и К в схеме.

После создания элемента, как и в предыдущих случаях, следует проверить его работоспособность, а также написать VHDL-программу, в тексте программы вместо сигналов J и K указывается один сигнал Т, который при симуляции будут иметь вид единичного сигнала.

2.5 D – триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Рис. 19 — Схема D-триггера на основе RS-триггера

Создаем схему, изображенную на рис. 19. Проверяем работоспособность данной схемы (рис.20), результаты сравниваем с таблицей истинности для D-триггера (Табл. 6).

Таблица 6 — Таблица переходов D-триггера

C | D | Q(t) | Q(t+1) | Пояснения |

0 | * | 0 | 0 | Режим хранение информации |

0 | * | 1 | 1 | |

1 | 0 | * | 0 | Режим записи информации |

1 | 1 | * | 1 |

Рис. 20. Результат проверки работы D-триггера.

Вьетнамки | Таблица истинности и различные типы

Триггер — это электронная схема с двумя стабильными состояниями, которая может использоваться для хранения двоичных данных. Сохраненные данные можно изменить, применяя различные входные данные. Триггеры и защелки являются фундаментальными строительными блоками систем цифровой электроники, используемых в компьютерах, средствах связи и многих других типах систем. Оба используются в качестве элементов хранения данных. Это основной элемент хранения в последовательной логике. Но сначала давайте проясним разницу между защелкой и шлепанцем.

Флип-флоп с защелкой

Основное различие между защелкой и триггером — это стробирующий или синхронизирующий механизм.

Простыми словами. Триггер срабатывает по фронту, а защелка срабатывает по уровню.

Полное сравнение триггеров с защелкой читайте здесь

Например, поговорим о защелках SR и триггерах SR. В этой схеме, когда вы устанавливаете S как активный, выход Q будет высоким, а Q ’будет низким. Это независимо ни от чего. (Это цепь с активным низким уровнем, поэтому активный здесь означает низкий уровень, но для цепи с активным высоким уровнем активный означает высокий уровень)

Защелка SRТриггер, с другой стороны, является синхронным и также известен как защелка SR с синхронизацией или синхронизацией.

SR Flip-FlopНа этой принципиальной схеме выход изменяется (т. Е. Изменяются сохраненные данные) только тогда, когда вы подаете активный тактовый сигнал. В противном случае, даже если S или R активны, данные не изменятся. Давайте посмотрим на типы шлепанцев, чтобы лучше понять.

SR Вьетнамки

Существует четыре основных типа триггеров, наиболее распространенным из которых является SR-триггер. Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). В этой системе, когда вы устанавливаете «S» как активный, выход «Q» будет высоким, а «Q ‘ »будет низким.После того, как выходы установлены, подключение схемы сохраняется до тех пор, пока «S» или «R» не станут высокими, или пока не будет отключено питание. Как показано выше, он самый простой и легкий для понимания. Два выхода, как показано выше, противоположны друг другу. Таблица истинности SR Flip-Flop выделена ниже.

| S | R | Q | Q ’ |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | ∞ | ∞ |

JK Триггер

Из-за неопределенного состояния в триггере SR требуется другой триггер в электронике.Триггер JK является усовершенствованием триггера SR, где S = R = 1 не является проблемой.

JK Flip-FlopУсловие входа J = K = 1 дает выход, инвертирующий состояние выхода. Однако при практическом тестировании схемы выходы такие же.

Проще говоря, если входные данные J и K различаются (т.е. высокий и низкий), то выход Q принимает значение J на следующем фронте тактового сигнала. Если J и K оба низкие, то никаких изменений не происходит. Если J и K оба имеют высокий уровень на фронте тактового сигнала, выход будет переключаться из одного состояния в другое.JK Flip-Flops могут функционировать как Set или Reset Flip-flops

| Дж | К | Q | Q ’ |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

Флип-флоп D

ТриггерD — лучшая альтернатива, очень популярная в цифровой электронике.Они обычно используются для счетчиков, регистров сдвига и синхронизации входов.

D Flip-FlopВ этом случае выход может быть изменен только на фронте тактового сигнала, и если вход изменяется в другое время, выход не будет затронут.

| Часы | Д | Q | Q ’ |

| ↓ »0 | 0 | 0 | 1 |

| ↑ »1 | 0 | 0 | 1 |

| ↓ »0 | 1 | 0 | 1 |

| ↑ »1 | 1 | 1 | 0 |

Изменение состояния выхода зависит от нарастающего фронта тактового сигнала.Выход (Q) такой же, как и вход, и может изменяться только по нарастающему фронту тактового сигнала.

T Вьетнамки

T-триггер похож на JK-триггер. По сути, это версия триггеров JK с одним входом. Эта модифицированная форма триггера JK получается путем соединения обоих входов J и K. У него есть только один вход вместе с входом часов.

Эти триггеры называются T-триггерами из-за их способности дополнять свое состояние (т. Е.) Toggle, отсюда и название Toggle flip-flop.

| т | Q | Q (т + 1) |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

Применение триггеров

Это различные типы триггеров, используемых в цифровых электронных схемах, и области применения триггеров указаны ниже.

- Счетчики

- Делители частоты

- Регистры сдвига

- Регистры памяти

Эта статья была впервые опубликована 17 августа 2017 г. и обновлена 29 июня 2021 г.

Flip Flops, R-S, J-K, D, T, Master Slave

Цифровому компьютеру нужны устройства, которые могут хранить информацию. Триггер — это двоичное запоминающее устройство. Он может хранить двоичный бит 0 или 1. Он имеет два стабильных состояния HIGH и LOW, то есть 1 и 0. Он имеет свойство оставаться в одном состоянии неопределенно долго, пока входной сигнал не направит его на переключение в другое состояние.Его еще называют бистабильным мультивибратором.

Базовая форма триггера — хранить данные. Их можно использовать для записи или того, какое значение переменной (входное, выходное или промежуточное). Триггеры также используются для осуществления контроля над функциональностью цифровой схемы, то есть изменения работы схемы в зависимости от состояния одного или нескольких триггеров. Эти устройства в основном используются в ситуациях, когда требуется одно или несколько из этих трех.

Операции, хранение и последовательность.

Вьетнамки с защелкой

Триггер R-S (Reset Set) — самый простой из всех и наиболее легкий для понимания. По сути, это устройство, которое имеет два выхода, один из которых является инверсным или дополнительным по отношению к другому, и два входа. Импульс на одном из входов для перехода в определенное логическое состояние. Выходы будут оставаться в этом состоянии до тех пор, пока аналогичный импульс не будет подан на другой вход. Эти два входа называются входами Set и Reset (иногда называемыми входами предварительной настройки и сброса).

Такой триггер может быть сделан просто путем перекрестного соединения двух инвертирующих вентилей. Можно использовать вентиль И-НЕ или ИЛИ-ИЛИ. Рисунок 1 (a) показывает RS-триггер с вентилем И-НЕ, а Рисунок 1 (b) показывает ту же схему с вентилем ИЛИ-НЕ.

Рисунок 1: Триггер R-S с фиксацией с использованием логических вентилей И-НЕ и ИЛИ-ИЛИЧтобы описать схему на Рисунке 1 (а), предположим, что изначально оба R и S находятся в состоянии логической 1, а этот выход находится в состоянии логического 0.

Теперь, если Q = 0 и R = 1, то это состояния входов элемента B, поэтому выходы элемента B находятся на 1 (что делает его инверсией Q i.е. 0). Выход элемента B подключен к входу элемента A, поэтому, если S = 1, оба входа элемента A находятся в состоянии логической 1. Это означает, что выход вентиля A должен быть 0 (как было изначально указано). Другими словами, состояние 0 в Q постоянно отключает вентиль B, так что любое изменение в R не имеет никакого эффекта. Кроме того, состояние 1 в постоянно активирует вентиль A, так что любое изменение S будет передаваться через Q. Вышеупомянутые условия составляют одно из стабильных состояний устройства, называемое состоянием сброса, поскольку Q = 0.

Теперь предположим, что триггер RS в состоянии сброса, вход S переходит в 0. Выход элемента A, то есть Q, переходит в 1, а при Q = 1 и R = 1 выход элементов B () будет идти. до 0, теперь 0 вентиль A отключен, сохраняя Q в 1. Следовательно, когда S возвращается в состояние 1, это не влияет на триггер, тогда как изменение R вызовет изменение выходного сигнала вентиля B. Вышеупомянутые условия составляют другое стабильное состояние устройства, называемое состоянием Set, поскольку Q = 1. Обратите внимание, что изменение состояния S с 1 на 0 привело к переходу триггера из состояния Reset в состояние Set.

Есть еще одно условие ввода, которое еще не было рассмотрено. То есть, когда оба входа R и S переводятся в логическое состояние 0. Когда это произойдет, оба Q и будут принудительно установлены в 1 и будут оставаться до тех пор, пока R и S сохраняются в 0. Однако, когда оба входа возвращаются в 1 невозможно узнать, будет ли триггер зафиксирован в состоянии сброса или состояния установки. Условие называется неопределенным из-за этого неопределенного состояния. При использовании R-S-триггера необходимо проявлять большую осторожность, чтобы гарантировать, что оба входа не получают команды одновременно.

| Начальные условия | Входы (импульсные) | Окончательный результат | ||

|---|---|---|---|---|

| Q | S | R | Q | |

| 1 | 0 | 0 | неопределенный | |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | неопределенный | |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 |

или более просто показано в таблице 2

| S | R | Q |

|---|---|---|

| 0 | 0 | неопределенный |

| 0 | 1 | Комплект (1) |

| 1 | 0 | Сброс (0) |

| 1 | 1 | Без изменений |

Когда используется вентиль ИЛИ-НЕ, входы R и S транспонируются по сравнению с версией NAND.Также стабильное состояние, когда оба R и S равны 0. Изменение состояния осуществляется путем переключения соответствующего входа в состояние 1. Неопределенное состояние теперь — это когда оба R и S одновременно находятся на логической 1. Таблица 3 показывает эту операцию.

| S | R | Q |

|---|---|---|

| 0 | 0 | Без изменений |

| 0 | 1 | Сброс (0) |

| 1 | 0 | Комплект (1) |

| 1 | 1 | Неопределенный |

Триггер RS с тактовой частотой

Триггер с защелкой RS требует прямого ввода, но не требует часов.Очень полезно добавить часы, чтобы точно контролировать время, в которое триггер изменяет состояние своего выхода.

В синхронизированном триггере R-S соответствующие уровни, подаваемые на их входы, блокируются до получения импульса от другого источника, называемого тактовым сигналом. Триггер меняет состояние только при подаче тактового импульса в зависимости от входов. Базовая схема показана на рисунке 2. Эта схема образована добавлением двух логических элементов И на входах триггера R-S. Помимо управляющих входов Set (S) и Reset (R), есть также вход часов (C).

Рисунок 2: Тактовый триггер RS| Начальные условия | Входы (импульсные) | Окончательный результат | Комментарий | |

|---|---|---|---|---|

| Q | S | R | Q (т + 1) | Без изменений |

| 0 | 0 | 0 | 0 | Без изменений |

| 0 | 0 | 1 | 0 | прозрачный Q |

| 0 | 1 | 0 | 1 | Набор Q |

| 0 | 1 | 1 | ??? | неопределенный |

| 1 | 0 | 0 | 1 | Без изменений |

| 1 | 0 | 1 | 0 | прозрачный Q |

| 1 | 1 | 0 | 1 | Набор Q |

| 1 | 1 | 1 | ??? | неопределенный |

Таблица возбуждения для R-S триггера очень просто выводится, как показано ниже

| S | R | Q |

|---|---|---|

| 0 | 0 | Без изменений |

| 0 | 1 | Сброс (0) |

| 1 | 0 | Комплект (1) |

| 1 | 1 | Неопределенный |

Флип-флоп D

Тип D (триггер данных или задержки) имеет один вход данных в дополнение к входу часов, как показано на рисунке 3.

Рисунок 3: D-триггерПо сути, такой тип триггера является модификацией синхронизируемых триггеров RS из базового триггера-защелки, а элементы NOR модифицируют его в тактовый триггер RS. Вход D идет напрямую на вход S, а его дополнение через вентиль НЕ применяется ко входу R.

Этот вид триггера предотвращает достижение значения D на выходе до тех пор, пока не появится тактовый импульс. Действие схемы прямолинейно и выглядит следующим образом.

Когда тактовый сигнал низкий, оба логических элемента И отключены, поэтому D может изменять значения, не влияя на значение Q.С другой стороны, когда часы высоки, оба логических элемента И включены. В этом случае Q принудительно равняется D, когда часы снова становятся низкими, Q сохраняет или сохраняет последнее значение D. Таблица истинности для такого триггера приведена ниже в таблице 6.

| S | R | Q (т + 1) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Таблица возбуждения для D-триггера очень просто выводится, как показано ниже.

| S | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

Вьетнамки JK

Один из самых полезных и универсальных триггеров — это триггер JK. Уникальные особенности триггеров JK:

- Если оба входа J и K равны 1 и применяется тактовый импульс, то выход изменит состояние независимо от своего предыдущего состояния.

- Если оба входа J и K находятся в 0 и применяется тактовый импульс, выход не будет изменен. В работе триггера JK нет неопределенного условия, т.е. у него нет неоднозначного состояния. Принципиальная схема триггера JK показана на рисунке 4.

Когда J = 0 и K = 0

Эти входы J и K отключают вентили И-НЕ, поэтому тактовый импульс не влияет на триггер. Другими словами, Q возвращает последнее значение.

Когда J = 0 и K = 1,

Верхний вентиль И-НЕ отключен, нижний вентиль И-НЕ включен, если Q равен 1, поэтому триггер будет сброшен (Q = 0, = 1), если он еще не находится в этом состоянии.

Когда J = 1 и K = 0

Нижний вентиль И-НЕ отключен, а верхний вентиль И-НЕ включен, если он равен 1. В результате мы сможем установить триггер (Q = 1, = 0), если он еще не установлен

Когда J = 1 и K = 1

Если Q = 0, нижний логический элемент И-НЕ отключен, верхний вентиль И-НЕ включен.Это установит триггер, и, следовательно, Q будет равно 1. С другой стороны, если Q = 1, нижний логический элемент И-НЕ будет включен, и триггер будет сброшен, и, следовательно, Q будет равно 0. Другими словами, когда J и K равны оба являются высокими, тактовые импульсы вызывают переключение триггера JK. Таблица истинности для триггера JK приведена в таблице 8.

| Начальные условия | Входы (импульсные) | Окончательный результат | |

|---|---|---|---|

| Q | S | R | Q (т + 1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Таблица возбуждения для JK-триггера очень просто выводится, как указано в таблице 9.

| S | R | Q |

|---|---|---|

| 0 | 0 | Без изменений |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Переключить |

T Вьетнамки

Метод предотвращения неопределенного состояния, обнаруживаемого при работе триггера RS, состоит в том, чтобы обеспечить только один вход (вход T), например, триггер действует как тумблер.Переключить означает перейти на предыдущий этап, т.е. переключиться в противоположное состояние. Он может быть построен из синхронизированного RS-триггера с обратной связью от выхода ко входу, как показано на рисунке 5.

Рисунок 5: T-триггерТакой триггер также называется переключаемым триггером. В таком триггере последовательность чрезвычайно узких триггеров управляет входом T каждый раз, когда один из этих триггеров меняет стадию на выходе триггера. Например, Q перед срабатыванием триггера равно 0. Тогда верхний вентиль И включен, а нижний вентиль И отключен.Когда срабатывает триггер, это приводит к высокому уровню S на входе.

Это устанавливает выход Q на 1. Когда следующий триггер появляется в точке T, активируется нижний логический элемент И и триггер проходит на вход R, что приводит к сбросу триггера.

Поскольку каждый входящий триггер попеременно изменяется на входы установки и сброса, триггер переключается. Для создания одного цикла выходного сигнала требуется два триггера. Это означает, что выходной сигнал имеет половину частоты входного сигнала, иначе говоря, T-триггер делит входную частоту на два.Таким образом, такую схему также называют схемой деления на два.

Недостатком триггера является то, что состояние триггера после подачи триггерного импульса известно только в том случае, если известно предыдущее состояние. Таблица истинности для T-триггера приведена в таблице 7.

| Q n | т | Q n + 1 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Таблица возбуждения для T-триггера очень просто выводится, как показано в таблице 8.

| т | Q |

|---|---|

| 0 | Q n |

| 1 | n |

Обычно микросхемы T-триггера недоступны. Его можно построить с помощью триггера JK, RS или D. На рисунке 6 показано соотношение T-триггера с использованием JK-триггера.

Рисунок 7. Триггер JK & D, подключенный как T-триггерТриггер D-типа может быть изменен путем внешнего подключения как каскад T-типа, как показано на рисунке 7.Поскольку Q-логика используется в качестве D-входа, каждый тактовый импульс передается в каскад, противоположный выходу Q. Таким образом, каскад, имеющий Q — 0 транзисторов = 1, обеспечивает переключающее действие, если бы каскад имел Q = 1, тактовый импульс привел бы к передаче Q = 0, снова обеспечивая переключающее действие. Таким образом, триггер D-типа, подключенный, как показано на рисунке 6, будет работать как каскад T-типа, дополняя каждый тактовый импульс.

Триггеры Master Slave

На рисунке 8 показана принципиальная схема главного слэйва J-K триггера

. Рисунок 8: Главный-подчиненный JK-триггерРисунок 8: Главный-подчиненный JK-триггер

Главный-подчиненный триггер содержит два синхронизированных триггера.Первый называется ведущим, а второй ведомым. Когда часы высоки, мастер активен. Выход мастера устанавливается или сбрасывается в соответствии с состоянием входа. Поскольку ведомое устройство в этот период является информативным, его выход остается в предыдущем состоянии. Когда тактовая частота становится низкой, выходной сигнал ведомого триггера изменяется, потому что он становится активным в течение низкого периода тактовой частоты. Конечным выходом триггера «ведущий-ведомый» является выход ведомого триггера. Таким образом, выход триггера ведущего ведомого доступен в конце тактового импульса.

Что такое JK Flip Flop? Принципиальная схема и таблица истинности

Шлепанцы JK Flip Flop — наиболее широко используемые триггеры. Считается универсальной триггерной схемой. Последовательная работа JK-триггера такая же, как и для RS-триггера с тем же входом SET и RESET .

Разница в том, что JK-триггер не определяет недопустимые входные состояния RS-защелки (когда S и R оба равны 1). Название JK Flip Flop было сохранено на имени изобретателя схемы, известной как Jack Kilby.

Базовый символ JK Flip Flop показан ниже:

Базовый триггер RS с затвором NAND имеет две основные проблемы.

- Во-первых, следует избегать условия, когда S = 0 и R = 0.

- Во-вторых, если состояние S или R меняет свое состояние при высоком уровне входного сигнала, правильное действие фиксации не происходит.

Таким образом, для преодоления этих двух проблем RS Flip-Flop был разработан JK Flip-Flop.

JK Flip Flop — это, по сути, RS-триггер со стробированием с добавлением входной схемы синхронизации. Когда оба входа S и R равны логической «1», имеет место недопустимое условие.